X-Aurora TSUBASA

SX-Aurora TSUBASA Architecture Guide Revision 1.1

NEC CORPORATION, 2018

## About this document

This document covers the basic architecture of the NEC SX-Aurora TSUBASA series, including information on its software visible resources and instruction set.

This manual's content follows: Chapter 1 overview, Chapter 2 system overview. Software visible registers are covered in Chapter 3 and the data types and instruction formats used in NEC SX-Aurora TSUBASA are described in Chapter 4 and 5 respectively. The memory architecture are shown in Chapter 6, and Chapter 7 describes exceptions. The instruction set is described in Chapter 8. Some appendix information including SX-Aurora TSUBASA CPU microarchitecture overview is also provided in this document.

Copyright© 2018 NEC Corporation. All right reserved.

All information in this document is subject to change without notice.

All product, brand, or trade names in this publication are the trademarks or registered trademarks of their respective owners.

# Terminology

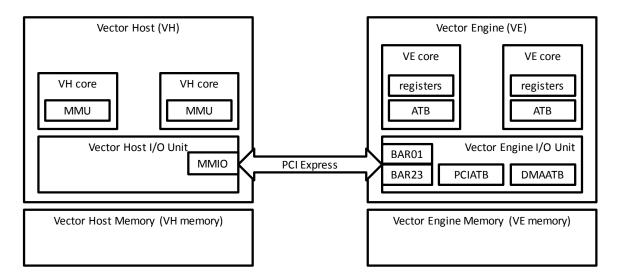

- VE: Vector Engine, NEC SX-Aurora TSUBASA's vector processing component. It is PCI express card form factored, consisting of multiple VE cores and the local HBM memory.

- VE core: the core component of the VE. It fetches codes and data from the VE memory, decodes and executes a program and write data to the VE memory, as its central processing unit. It also supports a native vector processing capability.

- VE memory: High bandwidth memory (HBM) inside the VE, mainly accessed by VE cores.

- VH: Vector Host, an x86 server to accommodate VEs inside. Currently Linux is supported for its operating system.

- VH CPU: CPUs for the VH server. Intel XEON CPU are currently supported.

- VI: Vector Island, a VH and VEs installed in the VE. It may have IB (Infiniband) HCAs for high performance data transfer.

# Contents

| 1. | Overview                                                                                             | 1-10 |

|----|------------------------------------------------------------------------------------------------------|------|

|    | 1.1. Overview                                                                                        | 1-10 |

| 2. | . Aurora Systems                                                                                     |      |

|    | 2.1. Single VI systems                                                                               |      |

|    | 2.1.1. 1-2 VE node systems                                                                           | 2-11 |

|    | 2.1.2. 4 VE node systems                                                                             |      |

|    | 2.1.3. 8 VE node systems                                                                             |      |

|    | 2.2. VI cluster systems                                                                              |      |

| 3. | . Registers                                                                                          |      |

|    | 3.1. Overview                                                                                        |      |

|    | 3.2. User Registers                                                                                  |      |

|    | 3.2.1. Process Status Word (PSW)                                                                     |      |

|    | 3.2.2. Instruction Counter (IC)                                                                      |      |

|    | 3.2.3. Scalar Register (S)                                                                           |      |

|    | 3.2.4. Vector Register (V)                                                                           |      |

|    | 3.2.5. Vector Mask Register (VM)                                                                     |      |

|    | 3.2.6. Vector Index Register (VIXR)                                                                  |      |

|    | 3.2.7. Vector Length Register (VL)                                                                   |      |

|    | 3.3. System Registers                                                                                |      |

|    | 3.3.1. Address Translation Buffer (ATB)                                                              |      |

|    | 3.3.2. Communication Register Directory (CRD)                                                        |      |

|    | 3.3.3. Communication Register (CR)                                                                   |      |

|    | 3.4. Performance Counters                                                                            |      |

| 4. | Data Format                                                                                          |      |

|    | 4.1 Data format                                                                                      |      |

|    | 4.1.1 Fixed-point data                                                                               |      |

|    | 4.1.2 Floating-Point Data                                                                            |      |

|    | 4.1.3 Logical Data                                                                                   |      |

|    | 4.2 Fixed-Point Arithmetic and Shift Operations                                                      |      |

|    | 4.2.1 Addition and Subtraction                                                                       |      |

|    | 4.2.2 Multiplication                                                                                 |      |

|    | 4.2.3 Division                                                                                       |      |

|    | 4.2.4 Comparison                                                                                     |      |

|    | 4.2.5 Compare and select operation                                                                   |      |

|    | 4.2.6 Arithmetic Shift                                                                               |      |

|    | 4.2.7 Logical Shift                                                                                  |      |

|    | 4.3 Floating-Point Arithmetic Operations                                                             |      |

|    | 4.3.1 Addition and Subtraction                                                                       |      |

|    | 4.3.2 Multiplication                                                                                 |      |

|    | 4.3.3 Division                                                                                       |      |

|    | 4.3.4 Square Root                                                                                    |      |

|    | 4.3.5 Fused multiply add                                                                             |      |

|    | 4.3.6 Reciprocal Approximation                                                                       |      |

|    | 4.3.7 Reciprocal Square Root Approximation                                                           |      |

|    | 4.3.8 Comparison                                                                                     |      |

|    | <ul><li>4.3.9 Compare and select operation</li><li>4.4 Format Conversion</li></ul>                   |      |

|    |                                                                                                      |      |

|    |                                                                                                      |      |

|    | · · · · · · · · · · · · · · · · · · ·                                                                |      |

|    | <ul><li>4.1.3. Floating-point data to Floating-point data</li><li>4.4 Arithmetic Exception</li></ul> |      |

|    | 4.4.1 Floating-point overflow                                                                        |      |

|    | 4.4.1 Floating-point overnow                                                                         |      |

|    | 4.1.4. Floating-point undernow                                                                       |      |

|    | 4.1.6. Division by zero                                                                              |      |

|    |                                                                                                      |      |

| 4.1.7.           | Invalid operation            |     |

|------------------|------------------------------|-----|

| 4.1.8.           | Inexact                      |     |

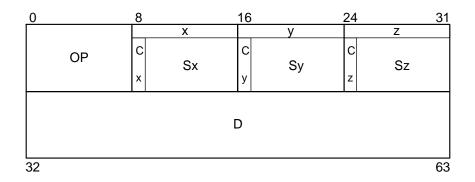

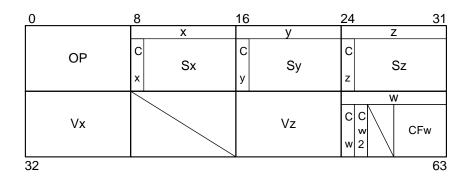

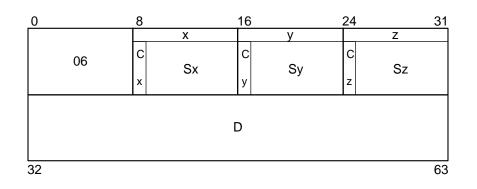

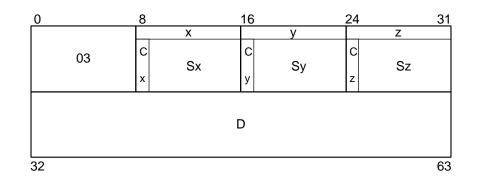

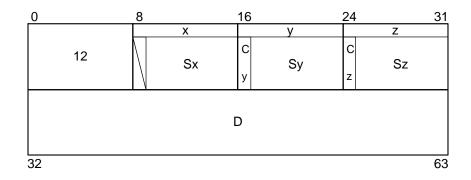

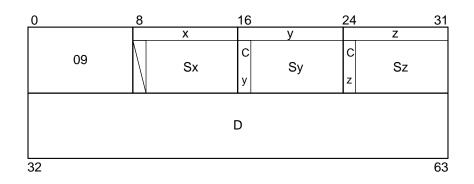

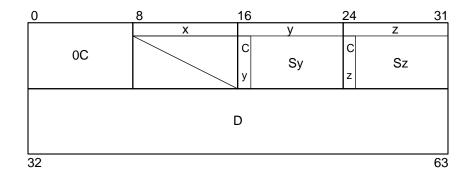

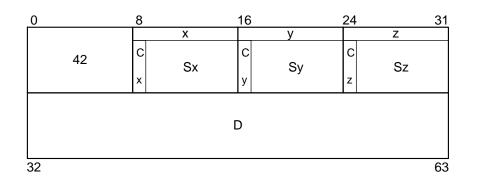

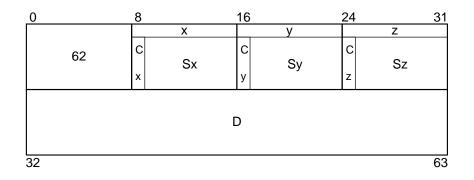

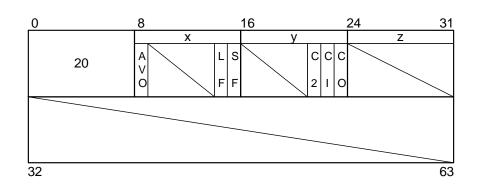

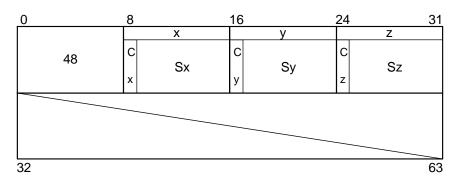

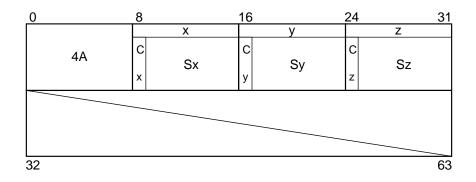

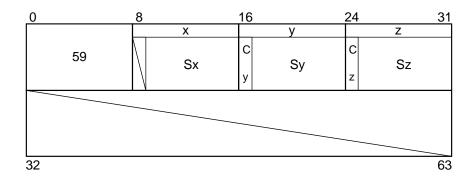

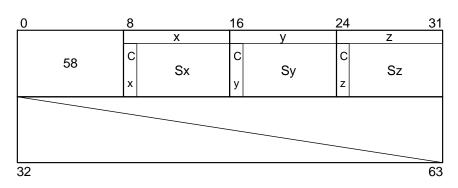

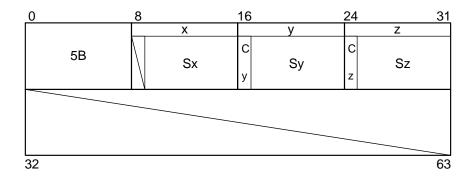

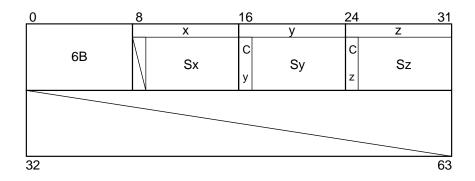

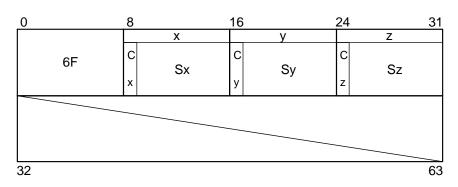

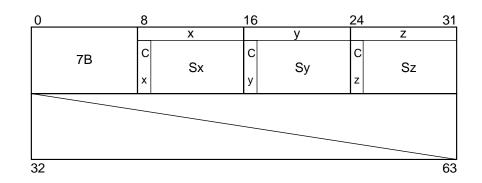

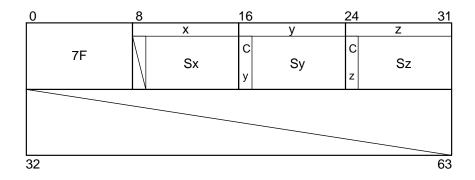

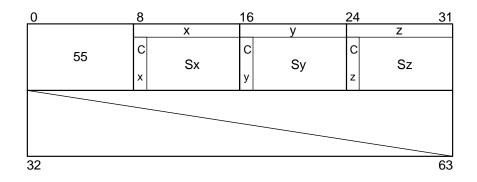

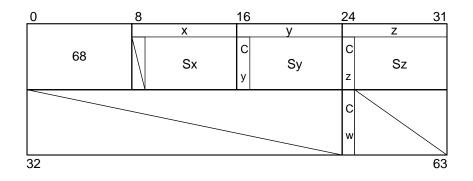

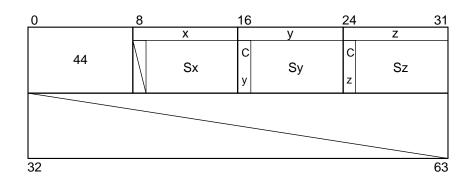

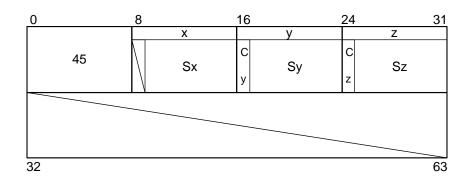

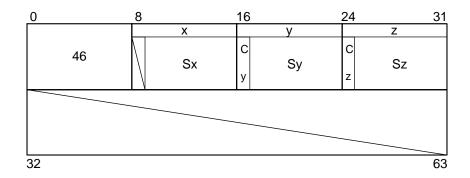

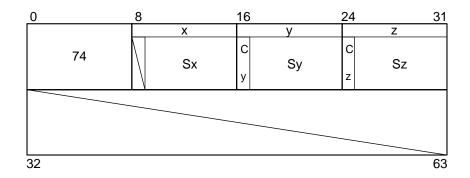

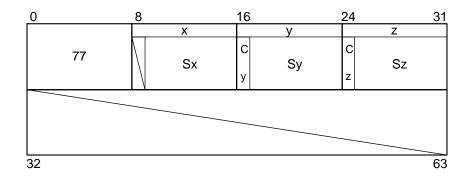

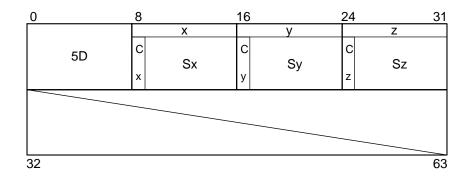

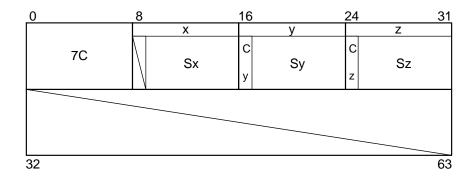

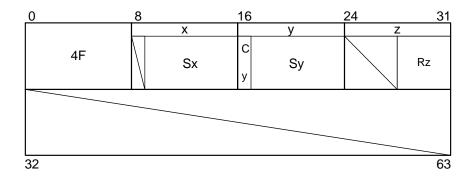

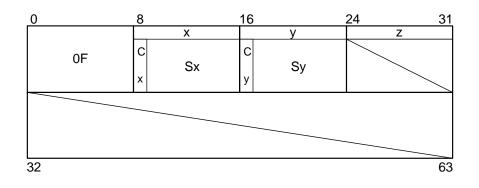

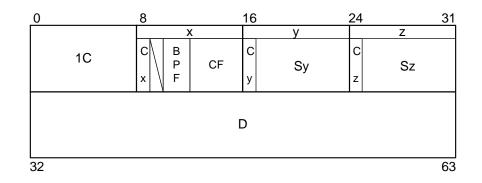

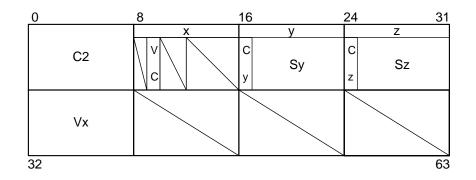

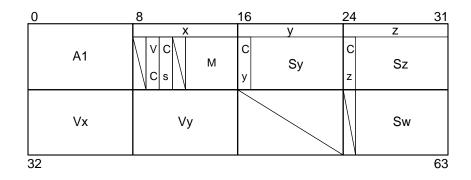

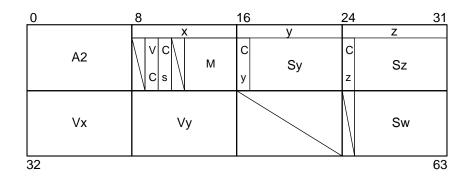

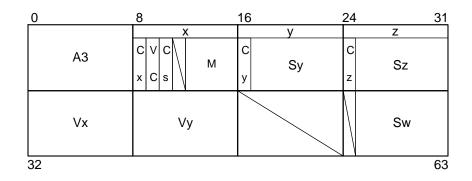

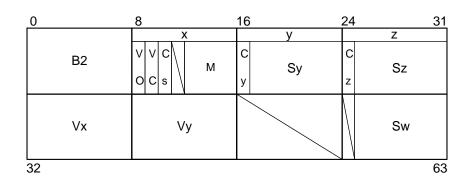

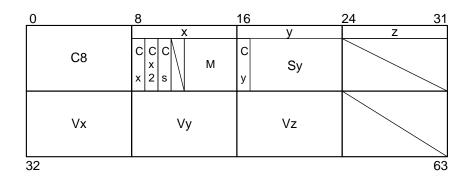

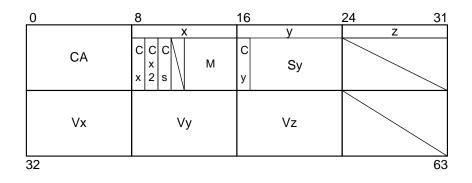

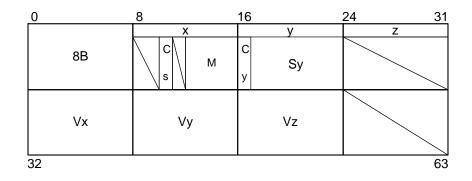

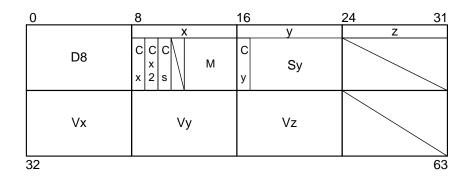

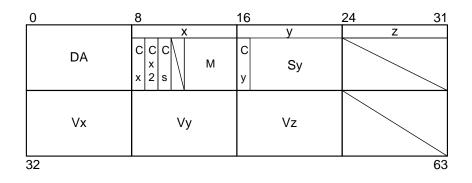

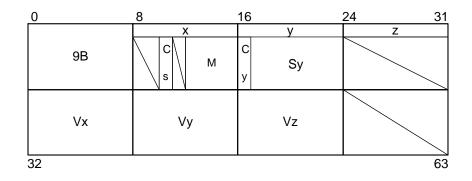

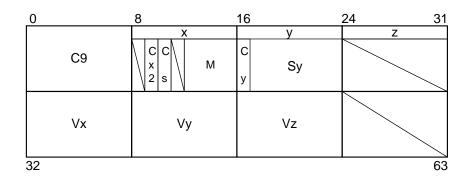

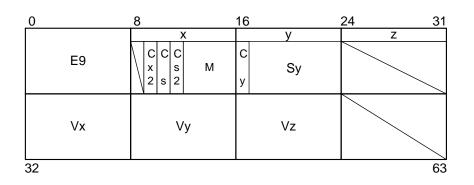

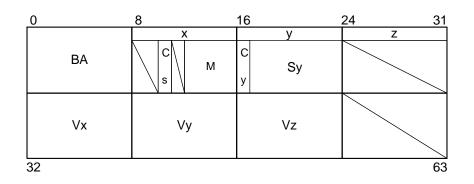

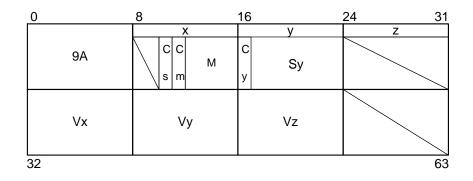

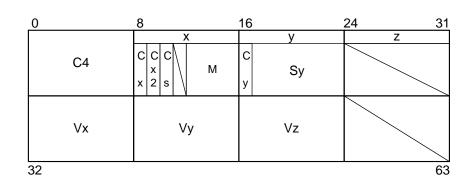

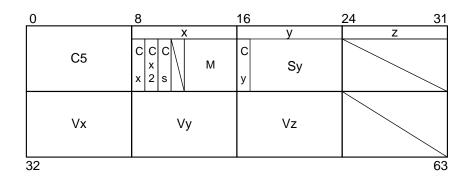

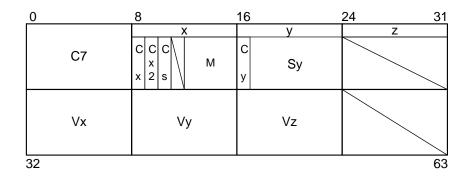

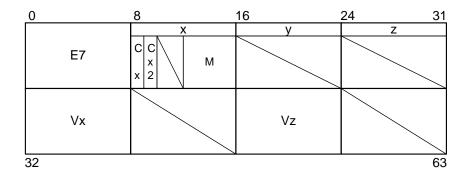

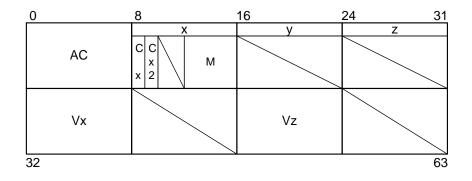

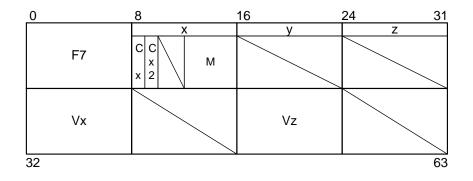

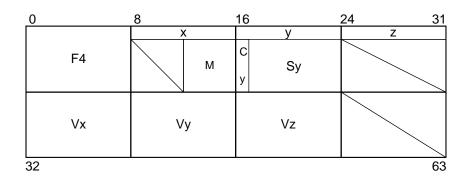

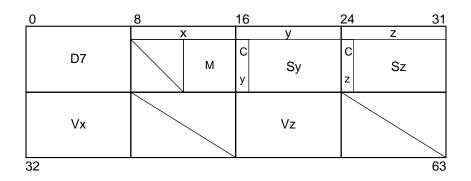

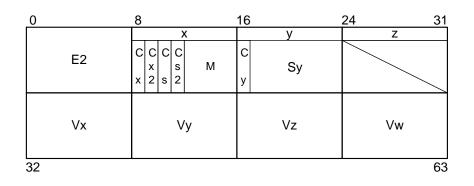

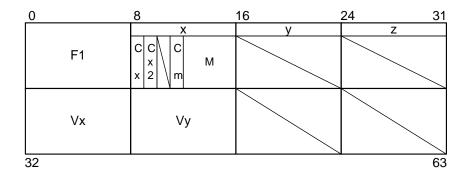

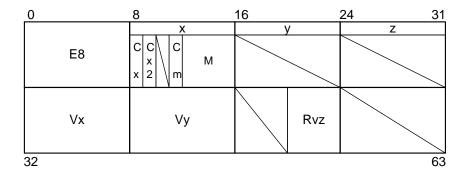

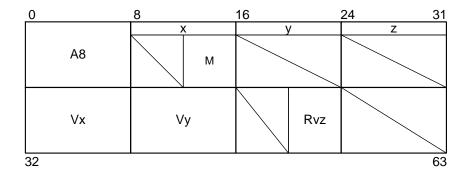

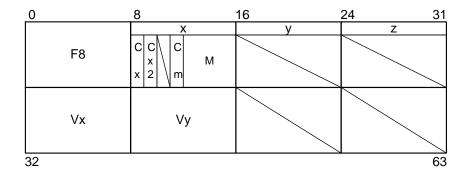

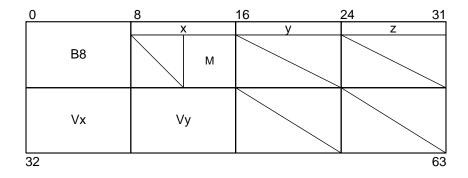

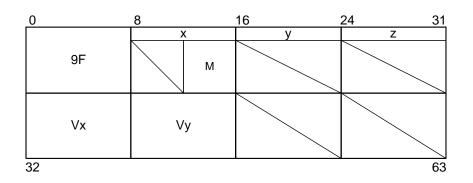

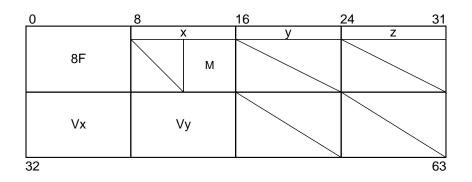

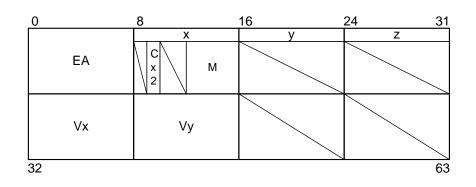

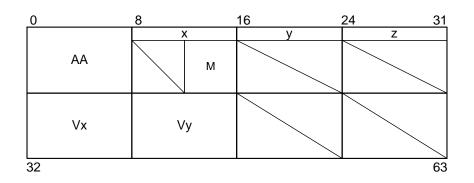

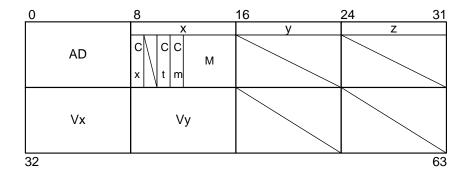

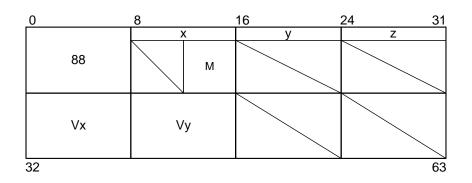

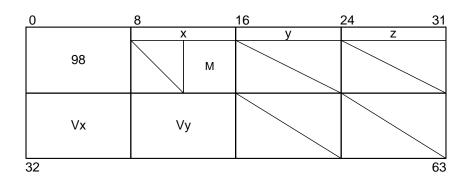

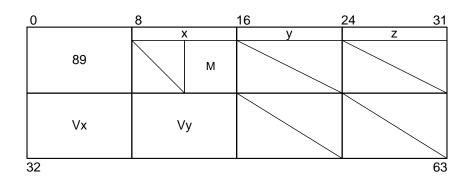

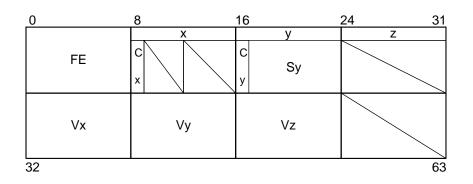

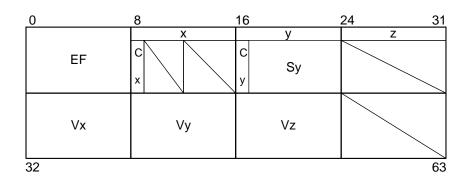

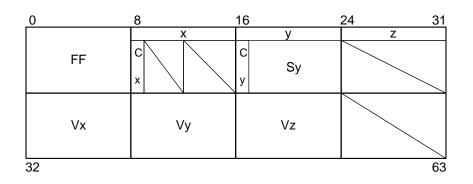

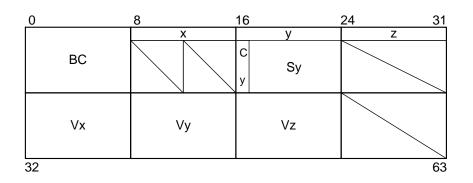

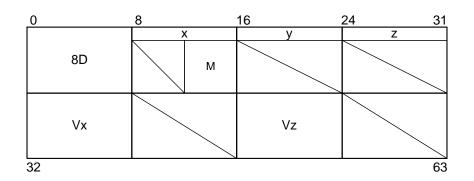

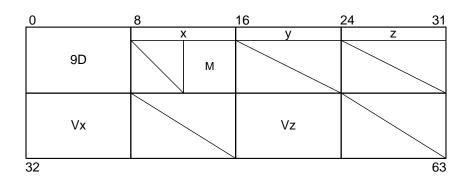

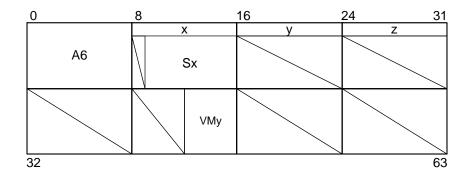

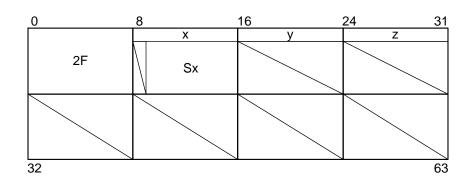

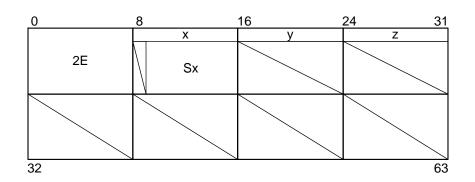

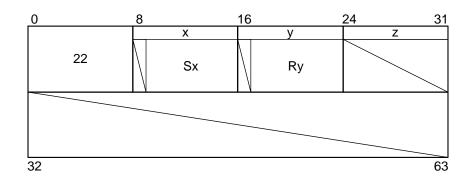

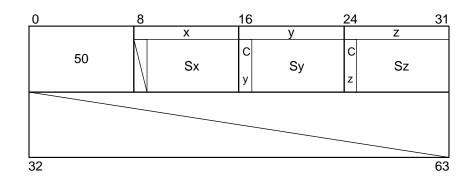

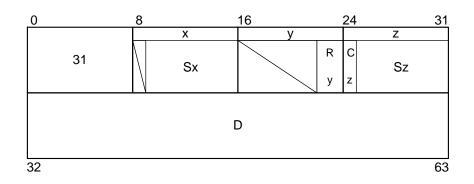

| 5. Instructi     | on Format                    | 5-0 |

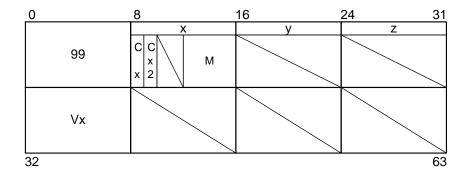

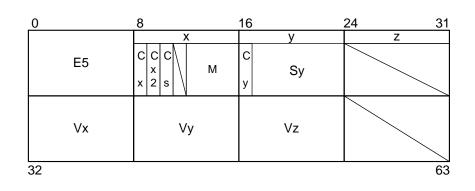

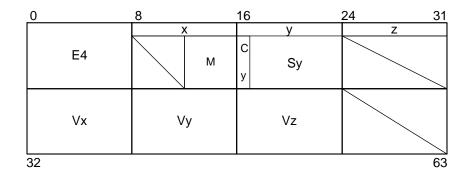

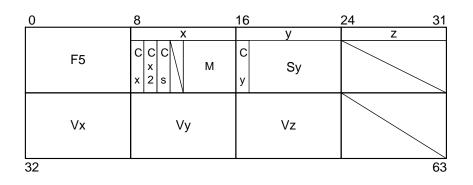

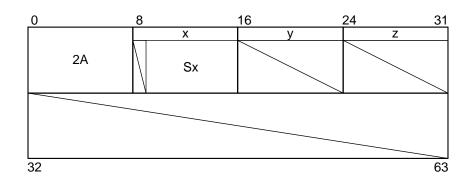

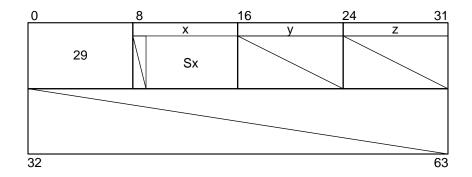

| RM Type.         |                              | 5-0 |

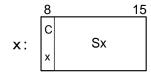

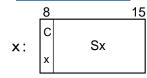

| 5.1.1.           | RM type x field              | 5-1 |

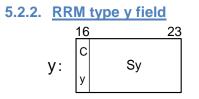

| 5.1.2.           | RM type y field              | 5-2 |

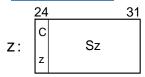

| 5.1.3.           | RM type z field              | 5-2 |

| 5.1.4.           | RM type D field              |     |

| 5.1.5.           | Effective Address            |     |

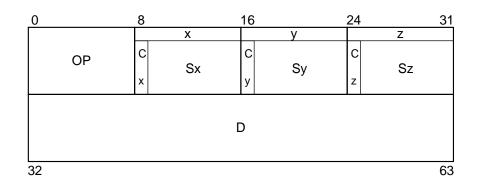

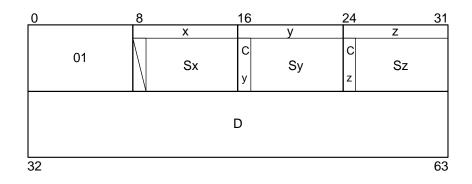

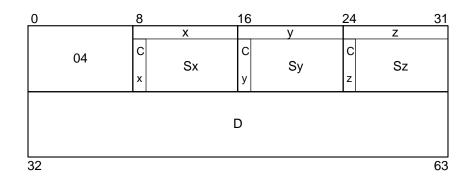

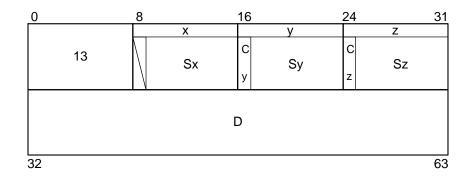

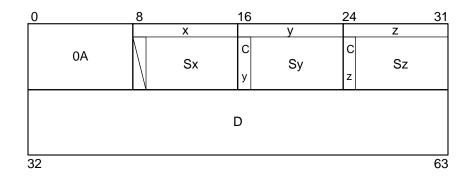

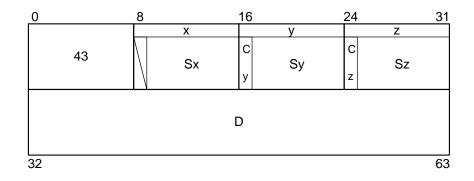

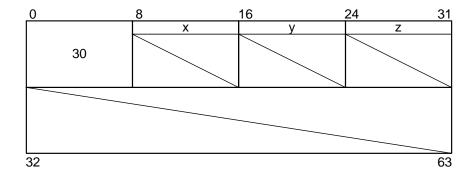

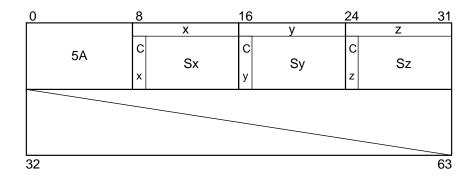

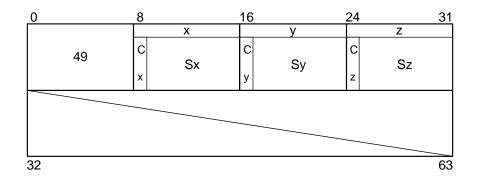

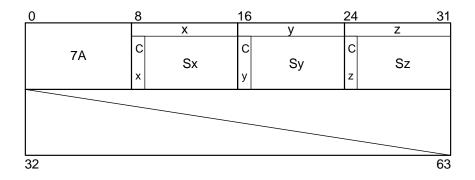

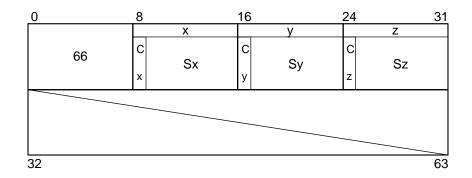

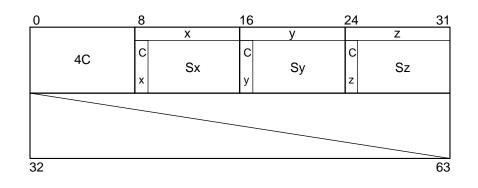

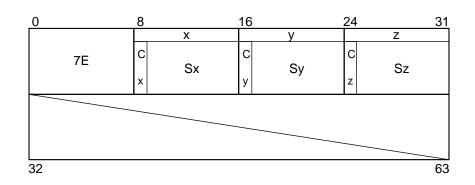

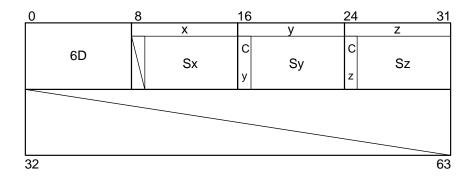

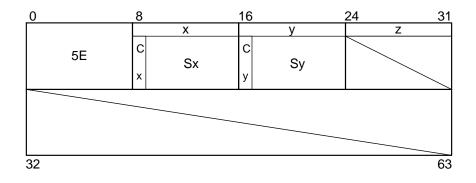

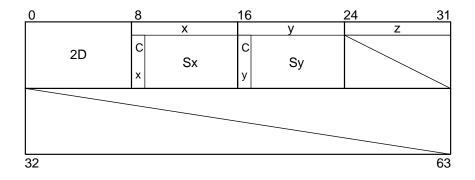

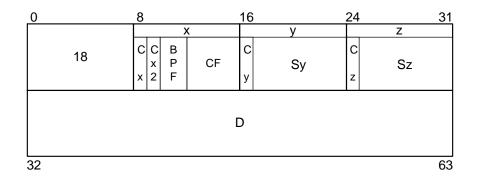

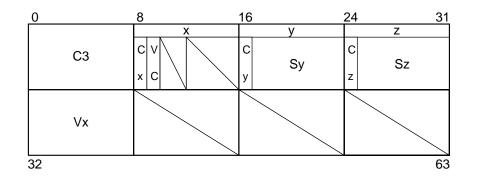

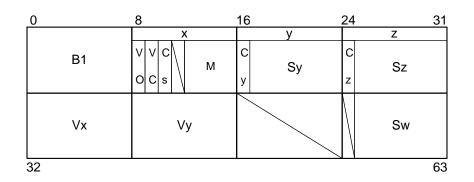

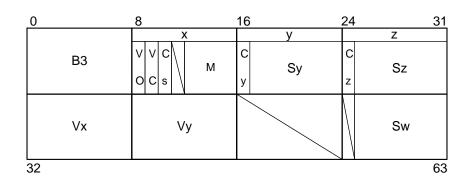

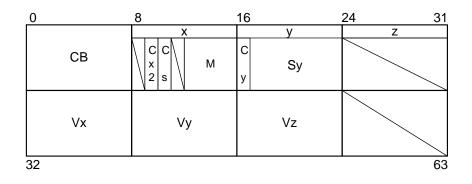

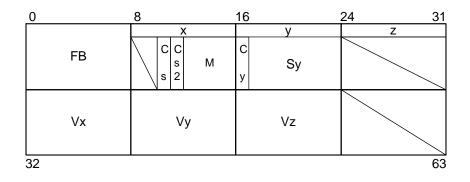

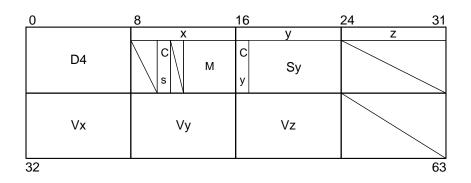

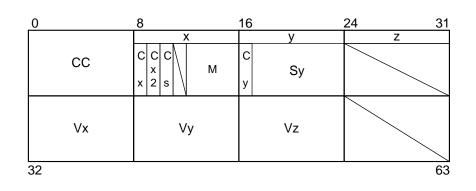

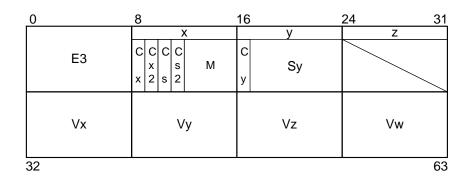

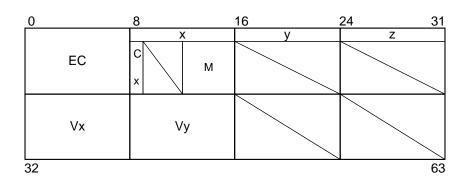

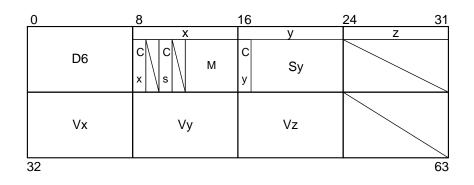

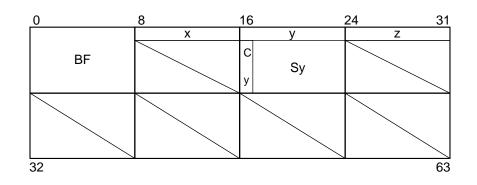

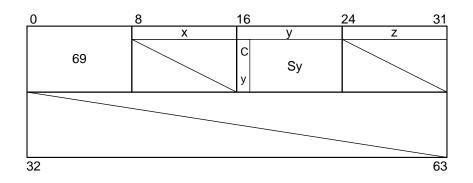

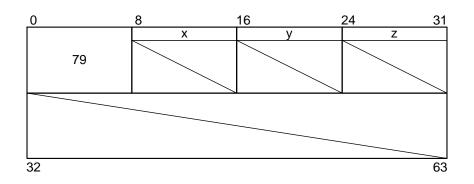

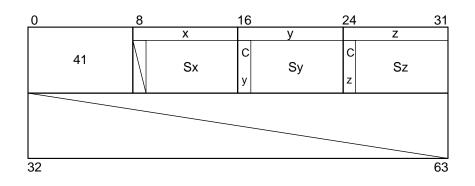

| 5.2. RR          | М Туре                       |     |

| 5.2.1.           | RRM type x field             |     |

| 5.2.2.           | RRM type y field             |     |

| 5.2.3.           | RRM type z field             |     |

| 5.2.4.           | RRM type D field             |     |

| 5.2.5.           | Effective Address            |     |

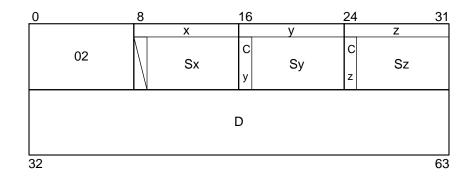

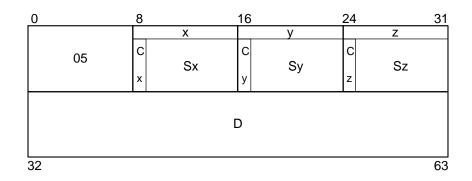

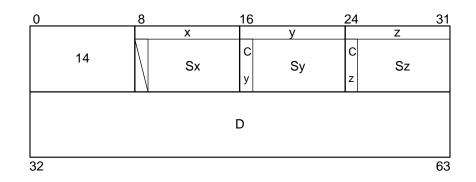

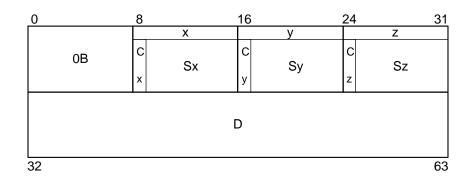

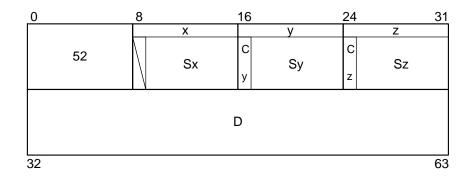

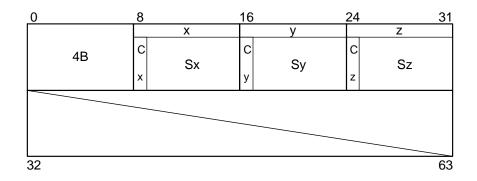

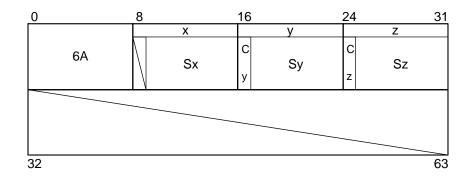

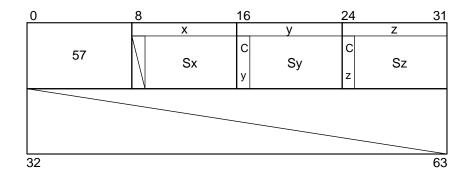

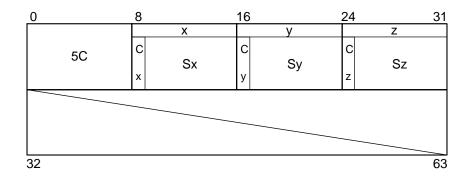

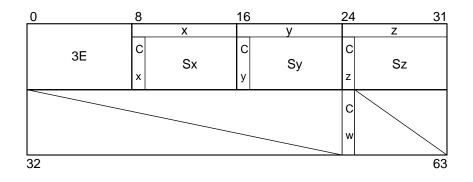

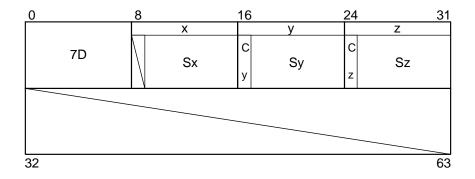

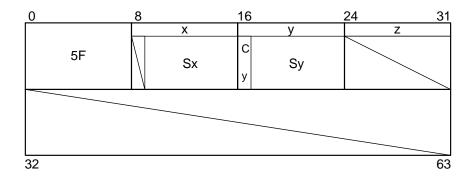

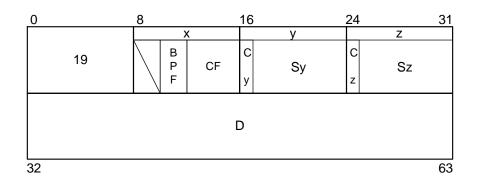

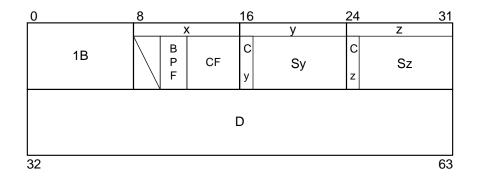

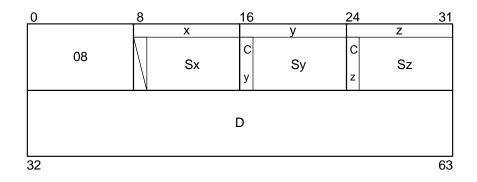

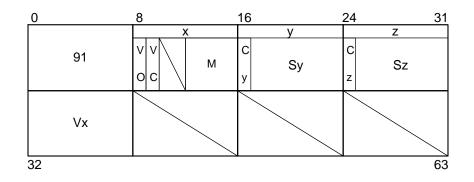

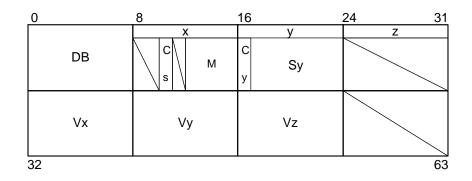

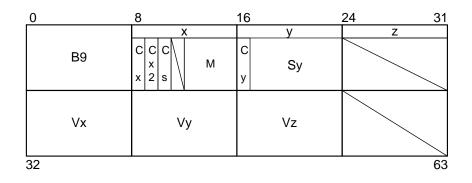

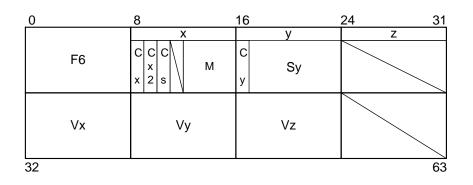

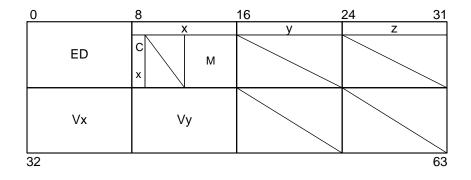

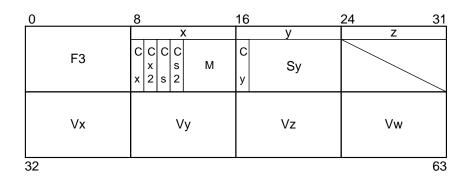

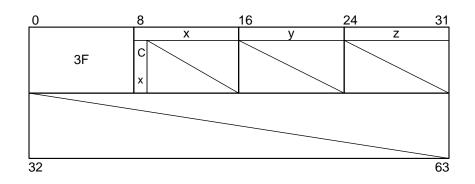

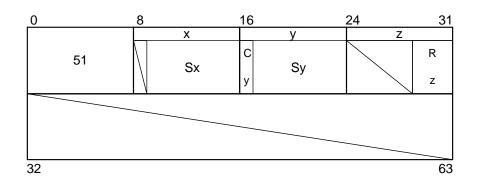

|                  | <br>Туре                     |     |

| 5.3.1.           | CF type x field              |     |

| 5.3.2.           | CF type y field              |     |

| 5.3.3.           | CF type z field              |     |

| 5.3.4.           | CF type D field              |     |

| 5.3.5.           | Effective Address            |     |

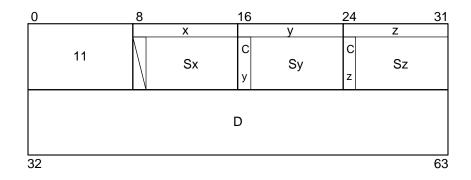

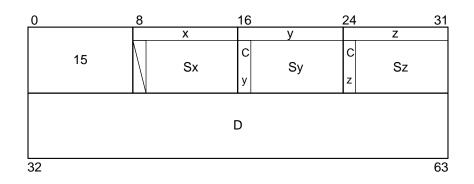

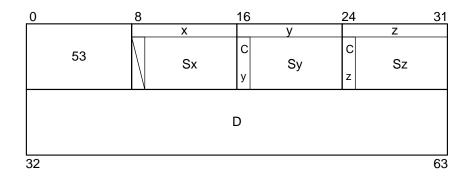

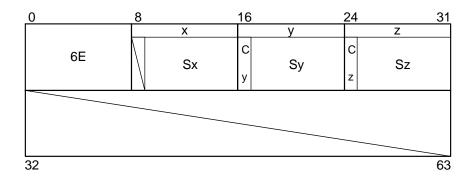

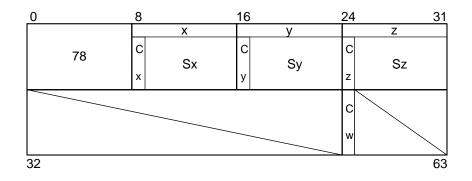

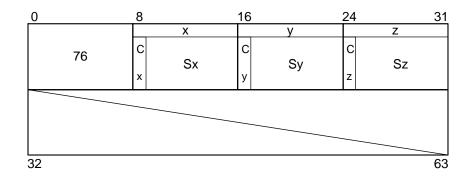

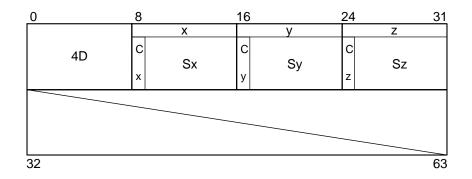

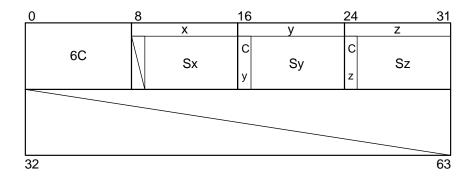

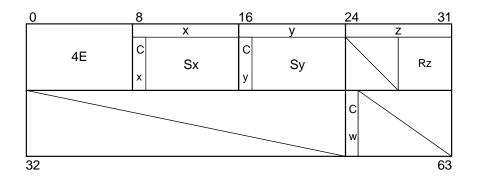

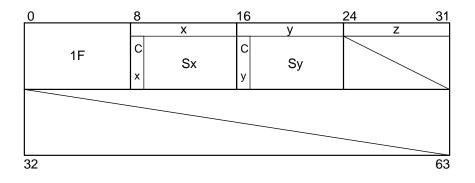

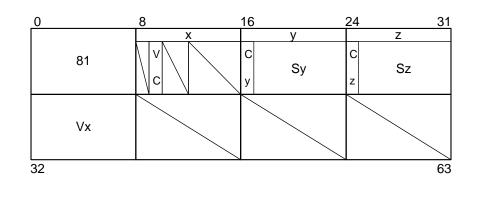

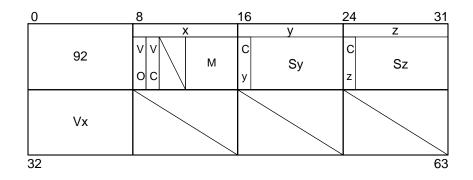

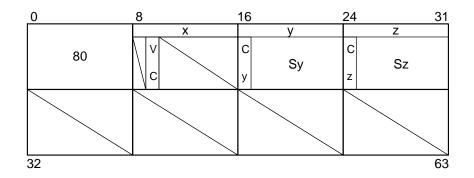

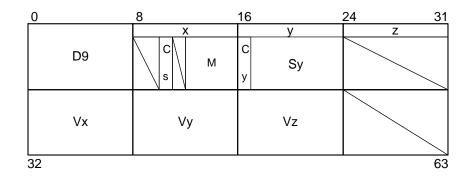

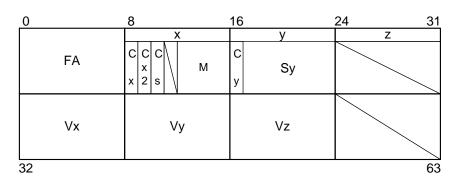

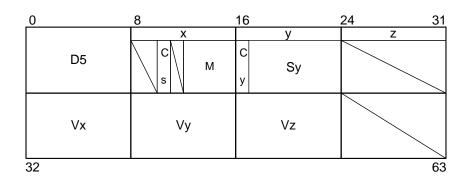

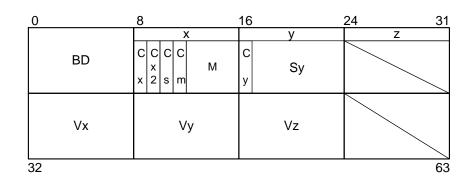

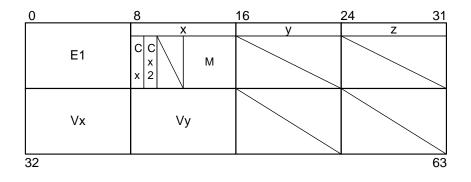

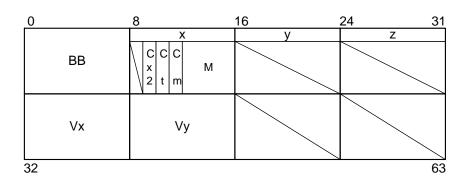

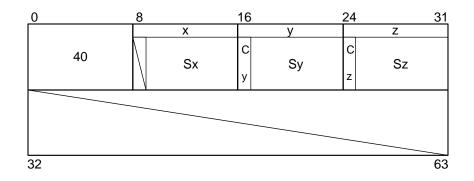

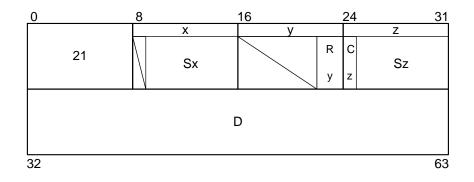

|                  | Type                         |     |

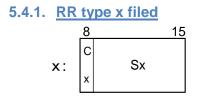

| 5.4.1.           | RR type x filed              |     |

| 5.4.1.           | RR type y field              |     |

| 5.4.2.<br>5.4.3. |                              |     |

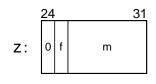

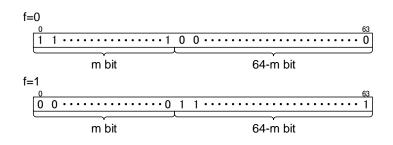

|                  | RR type z field              |     |

| 5.4.4.           | RR type w field              |     |

| 5.4.5.           | RR type Vx and Vz field      |     |

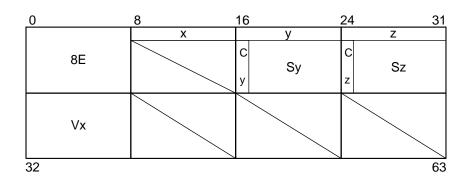

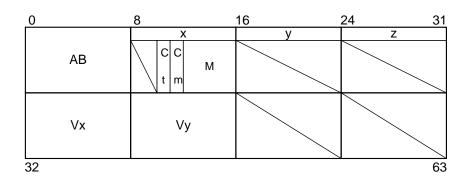

|                  | / Type                       |     |

|                  | M Type                       |     |

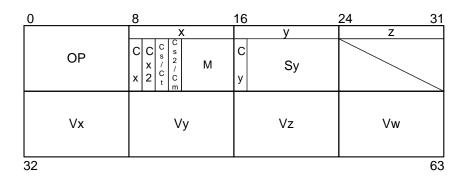

| 5.6.1.           | RVM type x field             |     |

| 5.6.2.           | RVM type y field             |     |

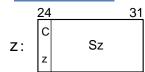

| 5.6.3.           | RVM type z field             |     |

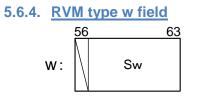

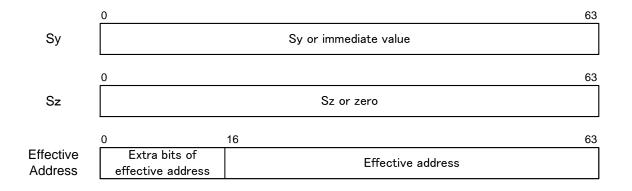

| 5.6.4.           | RVM type w field             |     |

| 5.6.5.           | RVM type Vx and Vy field     |     |

| 5.6.6.           | RVM type instruction         |     |

|                  | Туре                         |     |

| 5.7.1.           | RV type x field              |     |

| 5.7.2.           | RV type y field              |     |

| 5.7.3.           | RV type z field              |     |

| 5.7.4.           | RV type Vx, Vy, Vz, Vw field |     |

| 6. Memory        | Architecture                 | 6-0 |

|                  | mory Architecture Overview   |     |

| 6.2. Add         | dress Space                  | 6-1 |

| 6.2.1.           | Absolute address space       | 6-1 |

| 6.3. Typ         | es of Memory Access          | 6-3 |

| 6.3.1.           | VE core memory accesses      | 6-3 |

| 6.4. Add         | dress Translation            | 6-4 |

| 6.4.1.           | Page size                    | 6-4 |

| 6.4.2.           | Partial space                | 6-4 |

| 6.4.3.           | Address translation buffer   |     |

| 6.5. Me          | mory Access Ordering         |     |

| 6.5.1.           | Release consistency model    |     |

|                  | che Memory                   |     |

| 6.6.1.           | Cache hierarchy              |     |

| 6.6.2.           | Cache coherency              |     |

| 6.6.3.           | Cache control                |     |

| 6.6.4.           | Cache bypass                 |     |

| 0.01.11          |                              |     |

| 6.6.5.           | LLC                              | 6-12 |

|------------------|----------------------------------|------|

| 6.7. Cor         | mmunication Register             | 6-14 |

| 6.7.1.           | Access to CR                     | 6-14 |

| 6.7.2.           | Barrier synchronization using CR | 6-17 |

| 7. Exception     | ons                              |      |

| 7.1. Exc         | ceptions and interrupts          | 7-0  |

| 7.1.1.           | Attributes of interrupts         | 7-1  |

| 7.1.2.           |                                  |      |

| 7.1.3.           | •                                |      |

| 8. Instructi     | ons                              |      |

|                  | jends                            |      |

| 8.1.1.           | Desctiption of the function      |      |

| 8.1.2.           | Operators                        |      |

| 8.1.3.           | keywords and notations           |      |

| 8.1.4.           | Syntax                           |      |

| 8.1.5.           | Endianness                       |      |

| 8.1.6.           | Vector elements                  | 8-3  |

|                  | ad/Store instructions            |      |

| 8.2.1.           | LEA                              |      |

| 8.2.2.           | <br>LDS                          | -    |

| 8.2.3.           | LDU                              |      |

| 8.2.4.           | LDL                              |      |

| 8.2.5.           | LD2B                             |      |

| 8.2.6.           | LD1B                             |      |

| 8.2.7.           | STS                              | -    |

| 8.2.8.           | STU                              |      |

| 8.2.9.           | STL                              |      |

| 8.2.10.          | ST2B                             |      |

| 8.2.11.          | ST1B                             |      |

| 8.2.12.          | DLDS                             |      |

| 8.2.13.          | DLDU                             |      |

| 8.2.14.          | DLDL                             |      |

| 8.2.15.          | PFCH                             |      |

| 8.2.16.          | TS1AM                            |      |

| 8.2.17.          | TS2AM                            | -    |

| -                | TS3AM                            |      |

|                  | ATMAM                            |      |

|                  | CAS                              |      |

|                  | nsfer Control Instruction        |      |

| 8.3.1.           | FENCE                            |      |

| 8.3.2.           | SVOB                             |      |

| ••••             | ed-point Operation Instructions  |      |

| 8.4.1.           | ADD                              |      |

| 8.4.2.           | ADD                              |      |

| 8.4.3.           | ADS                              |      |

| 8.4.3.<br>8.4.4. | SUB                              |      |

| 8.4.4.<br>8.4.5. | SOBSOB                           |      |

| 8.4.5.<br>8.4.6. | SBS                              |      |

|                  | SBA<br>МРҮ                       |      |

| 8.4.7.<br>8.4.8. | MP Y<br>MPS                      |      |

| 8.4.8.<br>8.4.9. | MPS                              |      |

|                  |                                  |      |

| 8.4.10.          | MPD                              |      |

| 8.4.11.          | DIV                              |      |

| 8.4.12.          | DVS                              |      |

| 8.4.13.          | DVX                              |      |

| 8.4.14.          | CMP                              |      |

| 8.4.15.          | CPS                              | 8-56 |

| 8.4.16.          | СРХ                                   | 8-58  |

|------------------|---------------------------------------|-------|

| 8.4.17.          | CMS                                   | 8-59  |

| 8.4.18.          | CMX                                   | 8-60  |

| 8.5. Log         | ical Operation Instructions           | 8-61  |

| 8.5.1.           | AND                                   |       |

| 8.5.2.           | OR                                    | 8-62  |

| 8.5.3.           | XOR                                   | 8-63  |

| 8.5.4.           | EQV                                   |       |

| 8.5.5.           |                                       |       |

| 8.5.6.           | MRG                                   |       |

| 8.5.7.           | LDZ                                   |       |

| 8.5.8.           | PCNT                                  |       |

| 8.5.9.           | BRV                                   |       |

| 8.5.10.          | BSWP                                  |       |

| 8.5.11.          | CMOV                                  |       |

|                  | ft Operation Instruction              |       |

| 8.6.1.           | SLL                                   |       |

| 8.6.2.           | SLD                                   |       |

| 8.6.3.           | SRL                                   |       |

|                  |                                       |       |

| 8.6.4.           | SRD                                   |       |

| 8.6.5.           | SLA                                   |       |

| 8.6.6.           | SLAX                                  |       |

| 8.6.7.           | SRA                                   |       |

| 8.6.8.           | SRAX                                  |       |

|                  | ating-Point Arithmetic Instructions   |       |

| 8.7.1.           | FAD                                   |       |

| 8.7.2.           | FSB                                   |       |

| 8.7.3.           | FMP                                   |       |

| 8.7.4.           | FDV                                   |       |

| 8.7.5.           | FCP                                   |       |

| 8.7.6.           | FCM                                   |       |

| 8.7.7.           | FAQ                                   |       |

| 8.7.8.           | FSQ                                   |       |

| 8.7.9.           | FMQ                                   |       |

| 8.7.10.          | FCQ                                   |       |

| 8.7.11.          | FIX                                   | 8-101 |

|                  | FIXX                                  |       |

| 8.7.13.          | FLT                                   | 8-105 |

| 8.7.14.          | FLTX                                  | 8-106 |

| 8.7.15.          | CVS                                   | 8-107 |

| 8.7.16.          | CVD                                   | 8-109 |

| 8.7.17.          | CVQ                                   | 8-111 |

| 8.8. Bra         | nch Instructions                      | 8-113 |

| 8.8.1.           | BC                                    | 8-113 |

| 8.8.2.           | BCS                                   | 8-115 |

| 8.8.3.           | BCF                                   |       |

| 8.8.4.           | BCR                                   |       |

| 8.8.5.           | BSIC                                  |       |

|                  | ctor Load/Store and Move Instructions |       |

| 8.9.1.           | VLD                                   |       |

| 8.9.2.           | VLDU                                  |       |

| 8.9.3.           | VLDL                                  |       |

| 8.9.4.           | VLD2D                                 |       |

| 8.9.4.<br>8.9.5. | VLDU2D                                |       |

| 8.9.6.           | VLDU2D                                |       |

| 8.9.7.           | VEDE2D                                |       |

|                  | VST                                   |       |

| 0.3.0.           |                                       |       |

|    | 8.9.9.             | VSTL                                         |      |     |

|----|--------------------|----------------------------------------------|------|-----|

|    | 8.9.10.            | VST2D                                        |      |     |

|    | 8.9.11.            | VSTU2D                                       |      |     |

|    | 8.9.12.            | VSTL2D                                       |      |     |

|    | 8.9.13.            | VGT                                          |      |     |

|    | 8.9.14.            | VGTU                                         | . 8- | 150 |

|    | 8.9.15.            | VGTL                                         | . 8- | 152 |

|    | 8.9.16.            | VSC                                          | . 8- | 154 |

|    | 8.9.17.            | VSCU                                         | . 8- | 156 |

|    | 8.9.18.            | VSCL                                         |      |     |

|    | 8.9.19.            | PFCHV                                        | . 8- | 160 |

|    | 8.9.20.            | LSV                                          |      |     |

|    | 8.9.21.            | LVS                                          |      |     |

|    | 8.9.22.            | LVM                                          |      |     |

|    | 8.9.23.            | SVM                                          |      |     |

|    | 8.9.24.            | VBRD                                         |      |     |

|    |                    | VMV                                          |      |     |

| Q  |                    | ector Fixed-Point Arithmetic Instructions    |      |     |

| 0. | 8.10.1.            | VADD                                         |      |     |

|    | 8.10.1.            |                                              |      |     |

|    | 8.10.2.<br>8.10.3. | VADS<br>VADX                                 |      |     |

|    |                    |                                              | -    |     |

|    | 8.10.4.            | VSUB                                         |      |     |

|    | 8.10.5.            | VSBS                                         |      |     |

|    | 8.10.6.            | VSBX                                         |      |     |

|    | 8.10.7.            | VMPY                                         |      |     |

|    | 8.10.8.            | VMPS                                         |      |     |

|    | 8.10.9.            | VMPX                                         |      |     |

|    | 8.10.10.           | VMPD                                         |      |     |

|    | 8.10.11.           | VDIV                                         |      |     |

|    | 8.10.12.           | VDVS                                         |      |     |

|    | 8.10.13.           | VDVX                                         |      |     |

|    | 8.10.14.           | VCMP                                         |      |     |

|    | 8.10.15.           | VCPS                                         |      |     |

|    | 8.10.16.           | VCPX                                         |      |     |

|    | 8.10.17.           | VCMS                                         |      |     |

|    | 8.10.18.           | VCMX                                         | . 8- | 203 |

| 8. | 11. V              | ector Logical Operation Instructions         | . 8- | 205 |

|    | 8.11.1.            | VAND.                                        | . 8- | 205 |

|    | 8.11.2.            | VOR                                          | . 8- | 207 |

|    | 8.11.3.            | VXOR                                         | . 8- | 209 |

|    | 8.11.4.            | VEQV                                         | . 8- | 211 |

|    | 8.11.5.            | VLDZ                                         | . 8- | 213 |

|    |                    | VPCNT                                        |      |     |

|    |                    | VBRV                                         |      |     |

|    |                    | VSEQ                                         |      |     |

| 8  |                    | ector Shift Operation Instructions           |      |     |

| 0. | 8.12.1.            | VSLL                                         |      |     |

|    |                    | VSLD                                         |      |     |

|    |                    | VSRL                                         |      |     |

|    |                    | VSRD                                         |      |     |

|    |                    | VSRDVSLA                                     |      |     |

|    |                    | VSLAVSLAX                                    |      |     |

|    |                    |                                              |      |     |

|    |                    | VSRA                                         |      |     |

|    |                    | VSRAX                                        |      |     |

| 0  |                    | VSFA                                         |      |     |

|    |                    | ector Floating-Point Arithmetic Instructions |      |     |

|    | 8.13.1.            | VFAD                                         | . X- | Z34 |

| 8.13.2.  | VFSB                                   |       |

|----------|----------------------------------------|-------|

| 8.13.3.  | VFMP                                   | 8-240 |

| 8.13.4.  | VFDV                                   | 8-243 |

| 8.13.5.  | VFSQRT                                 | 8-246 |

| 8.13.6.  | VFCP                                   | 8-248 |

| 8.13.7.  | VFCM                                   |       |

| 8.13.8.  | VFMAD                                  |       |

| 8.13.9.  | VFMSB                                  |       |

| 8.13.10. |                                        |       |

|          |                                        |       |

| 8.13.11. |                                        |       |

| 8.13.12. |                                        |       |

| 8.13.13. |                                        |       |

| 8.13.14. | VFIX                                   | 8-270 |

| 8.13.15. | VFIXX                                  | 8-273 |

| 8.13.16. | VFLT                                   | 8-275 |

| 8.13.17. | VFLTX                                  | 8-278 |

| 8.13.18. |                                        |       |

| 8.13.19. |                                        |       |

|          | ector Reduction Instructions           |       |

| 8.14.1.  | VSUMS                                  |       |

| -        |                                        |       |

| 8.14.2.  | VSUMX                                  |       |

| 8.14.3.  | VFSUM                                  |       |

| 8.14.4.  | VMAXS                                  |       |

| 8.14.5.  | VMAXX                                  |       |

| 8.14.6.  | VFMAX                                  | 8-291 |

| 8.14.7.  | VRAND                                  | 8-294 |

| 8.14.8.  | VROR                                   | 8-295 |

| 8.14.9.  | VRXOR                                  | 8-296 |

|          | ector Iterative Operation Instructions |       |

| 8.15.1.  | VFIA                                   |       |

| 8.15.2.  | VFIS                                   |       |

|          |                                        |       |

| 8.15.3.  |                                        |       |

| 8.15.4.  | VFIAM                                  |       |

| 8.15.5.  | VFISM                                  |       |

| 8.15.6.  |                                        |       |

| 8.15.7.  | VFIMS                                  | 8-309 |

| 8.16. V  | ector Merger Operation Instructions    | 8-311 |

|          | VMRG                                   |       |

| 8.16.2.  | VSHF                                   | 8-313 |

| 8.16.3.  | VCP                                    | 8-315 |

|          | VEX                                    |       |

|          | ector Mask Operation Instructions      |       |

|          | VFMK                                   |       |

|          |                                        |       |

|          | VFMS                                   |       |

|          | VFMF                                   |       |

| 8.17.4.  |                                        |       |

| 8.17.5.  | ORM                                    |       |

| 8.17.6.  | XORM                                   | 8-327 |

| 8.17.7.  | EQVM                                   | 8-328 |

| 8.17.8.  | NNDM                                   | 8-329 |

| 8.17.9.  | NEGM                                   |       |

|          | PCVM                                   |       |

|          | LZVM                                   |       |

| 8.17.12. |                                        |       |

| -        | ector Control instructions             |       |

|          |                                        |       |

|          |                                        |       |

| 8.18.2.  | SVL                                    | 8-335 |

| 8.18.3. SM  | IVL                                    | 8-336 |

|-------------|----------------------------------------|-------|

| 8.18.4. LVI | Χ                                      | 8-337 |

| 8.19. Contr | ol Instructions                        |       |

| 8.19.1. SIC | 、<br>、                                 |       |

| 8.19.2. LPI | М                                      | 8-339 |

| 8.19.3. SPI | Μ                                      |       |

| 8.19.4. LFF | ۲                                      |       |

| 8.19.5. SFI | R                                      | 8-343 |

| 8.19.6. SM  | IIR                                    |       |

|             | P                                      |       |

| 8.19.8. MC  | )NC                                    |       |

|             | R                                      |       |

|             | SCR                                    |       |

|             | SCR                                    |       |

| 8.19.12. F  | FIDCR                                  |       |

|             | Memory Access Instructions             |       |

|             | М                                      |       |

|             | Μ                                      |       |

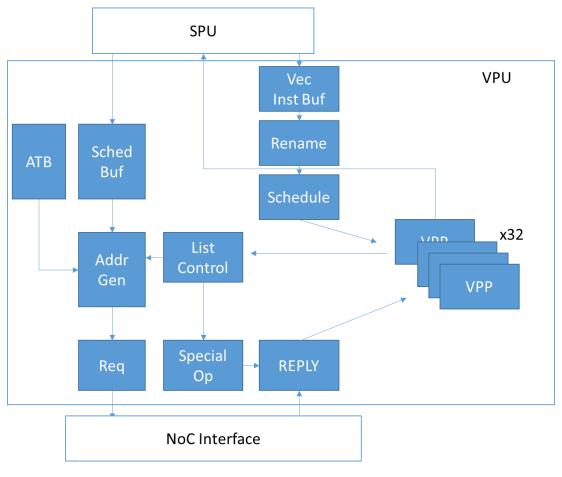

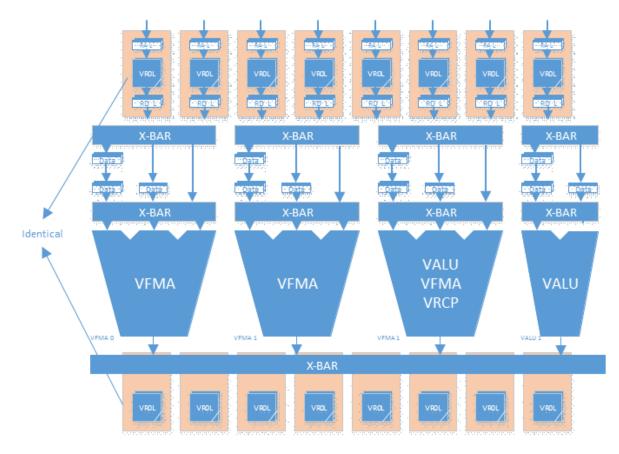

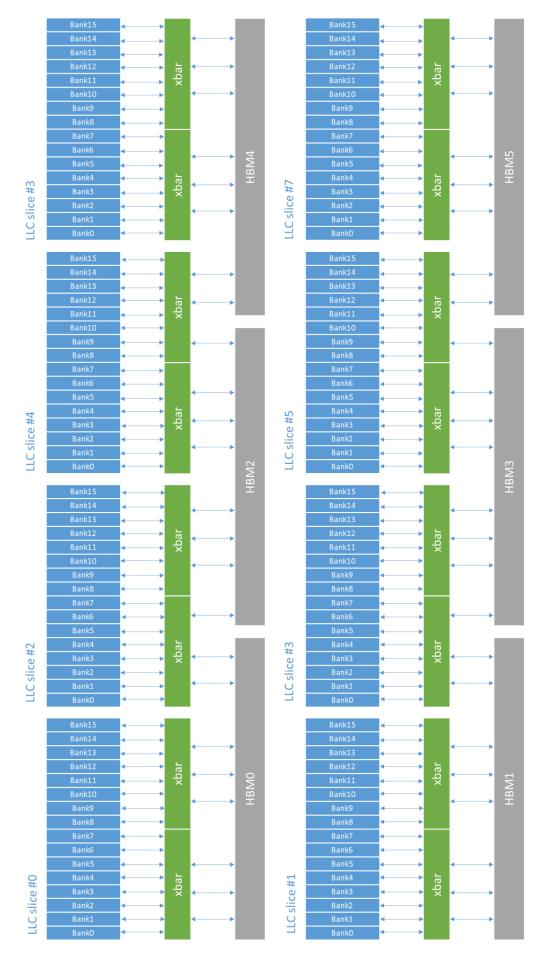

|             | Microarchitecture of SX-Aurora TSUBASA |       |

|             | J                                      |       |

|             |                                        |       |

|             |                                        |       |

|             |                                        |       |

| 0           | S                                      |       |

|             | nd VE memory                           |       |

|             |                                        |       |

|             |                                        |       |

|             |                                        |       |

|             |                                        |       |

|             | 2 List of Instructions                 |       |

|             | f SX-Aurora TSUBASA Instructions       |       |

|             | 3 Operation Code Table                 |       |

| 11.1. Opera | ation Code Table                       | 11-12 |

|             |                                        |       |

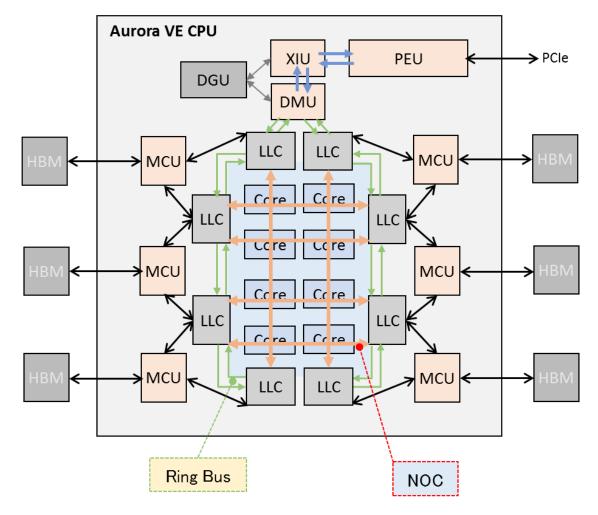

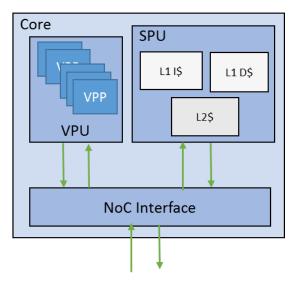

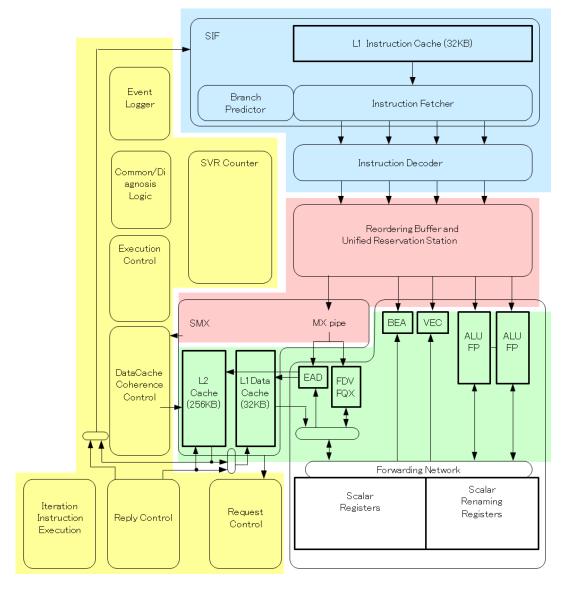

## 1. Overview

## 1.1. Overview

Simulation of natural or artificial processes has established itself as the third pillar in the fields of scientific research alongside theories and experiments. Especially in such as astrophysics, fluid/aerodynamics, applied/organic chemistry, pharmaceuticals and life science, supercomputing has been playing a major role and indispensable any more.

NEC's innovation platform SX-Aurora TSUBASA is designed to tackle such complex mathematical, scientific or engineering problems. The NEC proprietary computing systems provide complete solutions for all sorts of requirements by combining with a wealth of x86-based products and storage appliances.

NEC SX-Aurora Vector Engine (VE) is for accelerated computing exploiting vector computing technique proven by NEC's long history of supercomputing, on which a full application runs on high performance Vector Engines, and only system tasks are taken care of by the Vector Host (VH), a standard x86 server. With the vector computation mechanism, large memory bandwidth and a small number of powerful cores, the architecture gives a strong foundation for high sustained performance.

SX-Aurora TSUBASA Features:

- Eight vector cores, a peak performance of 2.45 TFLOPS

- Max 48 GB high bandwidth memory (HBM) with 1.2 TB/s memory bandwidth

- PCI express generation 3 x 16 lanes for VE-VH communication

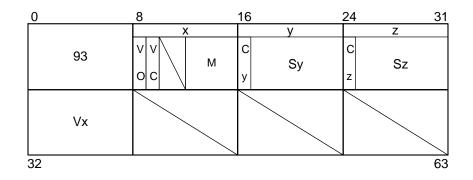

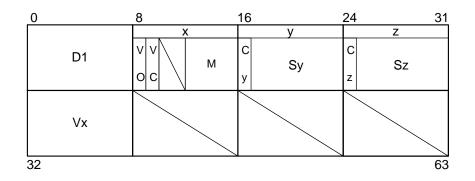

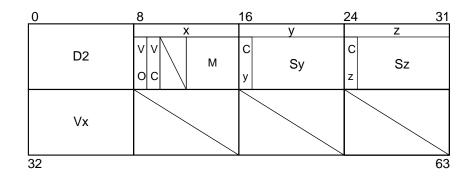

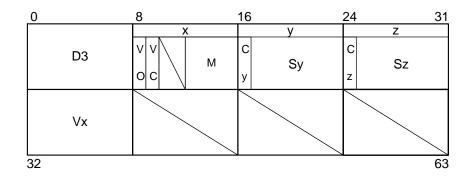

# 2. Aurora Systems

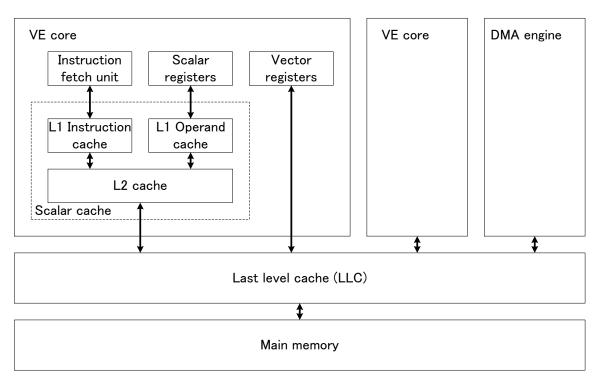

This chapter covers system overview. For generation specific microarchitecture please refer to Appendix SX-Aurora TSUBASA microarchitecture overview.

## 2.1. Single VI systems

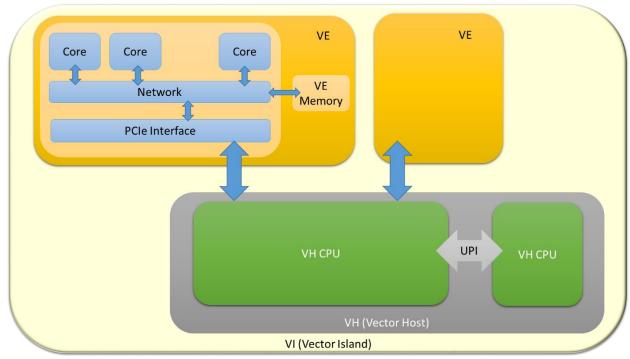

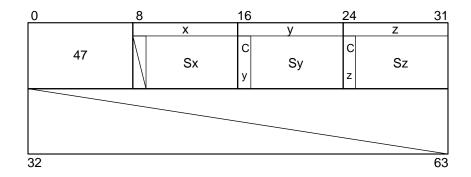

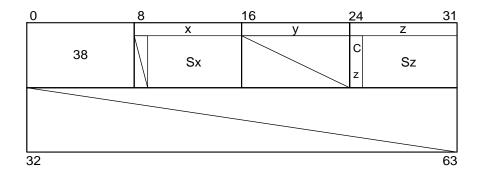

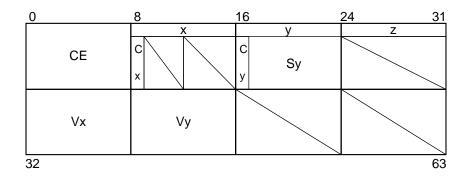

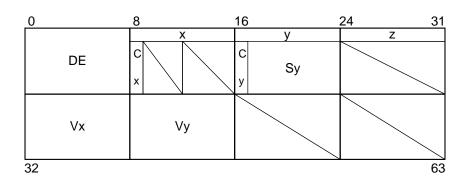

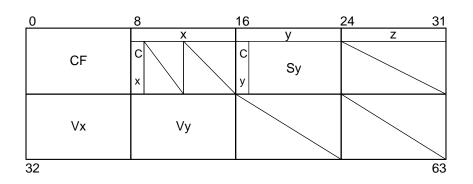

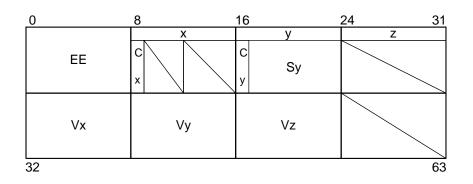

### 2.1.1. 1-2 VE node systems

For 1-2 node systems, one or two VEs and the VH form a VI (Vector Island). All VEs may be connected to PCIe slots from the one of VH CPUs.

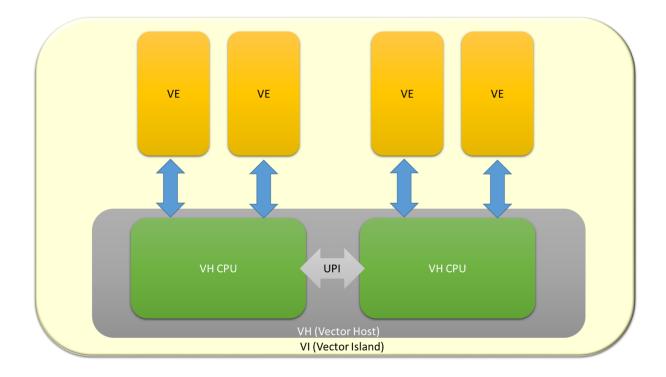

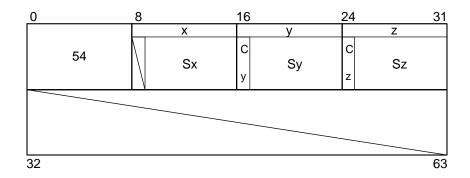

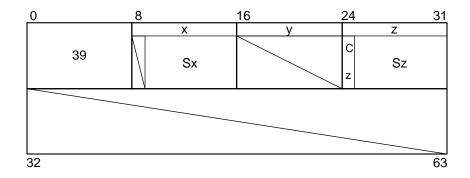

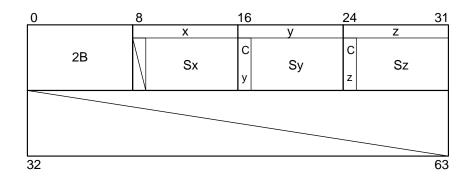

## 2.1.2. <u>4 VE node systems</u>

For four node systems, each two VEs are connected to a VH CPU and all VEs and VH CPUs form a VI.

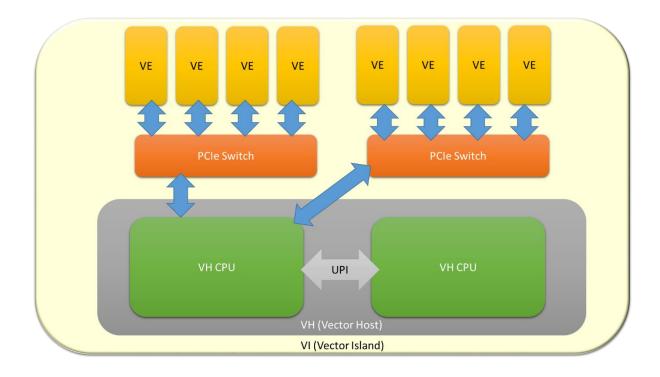

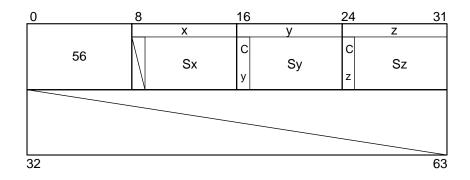

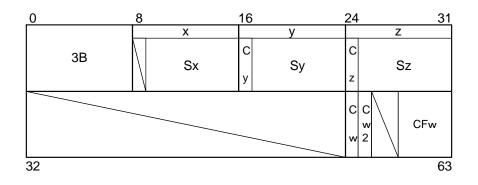

## 2.1.3. <u>8 VE node systems</u>

For eight node systems, each four VEs are connected to a PCIe switch. Two PCIe switches may be connected to the PCIe slots from a single VH CPU.

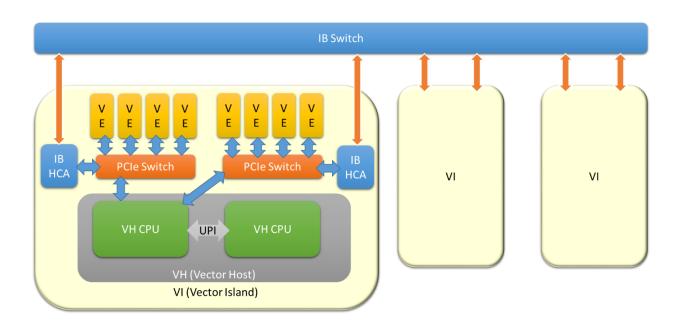

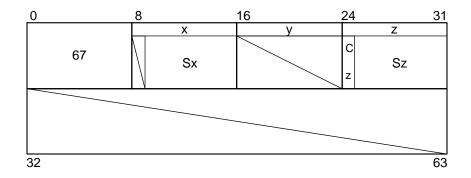

## 2.2. VI cluster systems

Any type of VIs is able to have IB (Infiniband) links by accommodating IB HCA card(s). Multiple VIs with IB link(s) can form a multi island configuration (VI cluster). A VI cluster is exampled on the figure above. IB links from VIs may be connected to the IB switch(es) for high performance computing support.

# 3. Registers

### 3.1. Overview

The Aurora system has three types of software visible registers, user registers, system registers and system common registers.

The user registers can be accessed by user processes running on a VE core. The system registers and system common registers are controlled by the VEOS on the VH, and the access to those registers from user processes is protected by its memory protection mechanism. The system registers are also used for resource protection in the Aurora system and are controlled by the resource manager of the VEOS. The system common registers are unique within a VE CPU and shared by all VE cores on the VE CPU, whereas each VE core has its own the user and system registers.

## 3.2. User Registers

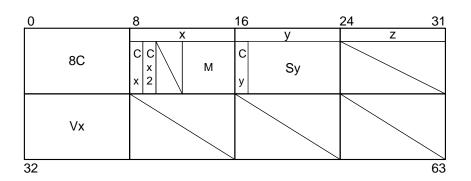

#### 3.2.1. Process Status Word (PSW)

The 64 bit process status word (PSW) indicates the status of a process running on the VE core. Each core has one PSW.

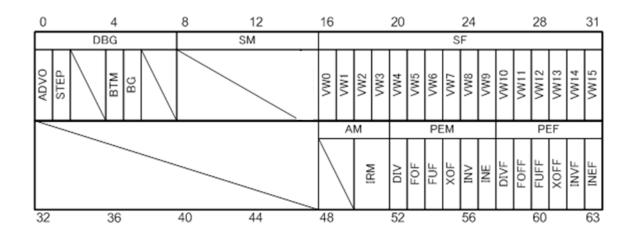

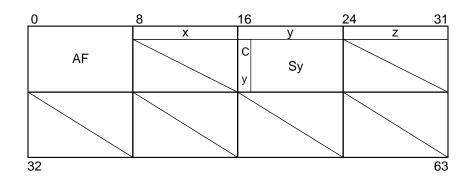

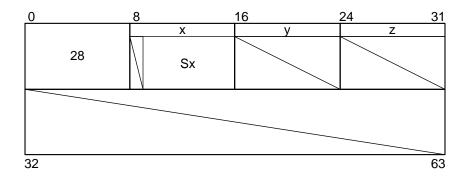

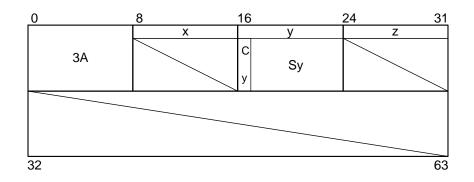

Figure 3-1 Process status word

Table 3-1 Process Status Word (1/3)

| Class               | PSW                     | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | bit                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Debug mode (DGB)    | 0<br>1<br>2-3<br>4<br>5 | <ul> <li>ADVO: Advance-off (lockstep execution) mode<br/>"0": Advance-off disabled (default)<br/>"1": Advance-off enabled. (Instruction execution is held until the<br/>preceding instruction(s) has completed.)</li> <li>STEP: One-step interrupt mode<br/>"0": One-step interrupt disabled (default)<br/>"1": One-step interrupt enabled. (An interrupt occurs and the<br/>process halts right after the current instruction completes.)</li> <li>RFU(Reserved for Future Use)</li> <li>BTM: Branch trap mode<br/>"0": Non-branch trap mode: branch trap exception interrupt is<br/>disabled (default)<br/>"1": Branch trap mode: branch trap exception interrupt is enabled.</li> <li>BG: Branch (No Go/Go) flag<br/>"0": indicates the result of the branch executed was NO-GO in the<br/>branch trap mode.<br/>"1": indicates the result of the branch executed was GO in the<br/>branch trap mode.</li> </ul> |

| System mode<br>(SM) | 6-7<br>8-15             | RFU<br>RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| System Flag (SF)    | 16-31                   | <ul> <li>VW0-15: Vector register write flag</li> <li>"0": Write to the corresponding vector register(s) hasn't occurred since this flag was reset.</li> <li>"1": Write to the corresponding vector register(s) has occurred since this flag was reset.</li> <li>VW0: V0-3</li> <li>VW1: V4-7 <ul> <li>:</li> <li>VW15: V60-63</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

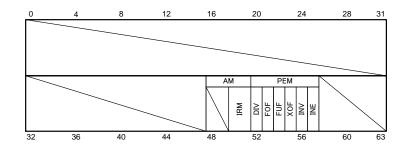

Table 3-2 Process Status Word (2/3)

| Class                        | PSW   | Meaning                                                                                                                                                                                                                                               |

|------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | bit   |                                                                                                                                                                                                                                                       |

|                              | 32-47 | RFU                                                                                                                                                                                                                                                   |

|                              | 48-49 | RFU                                                                                                                                                                                                                                                   |

| Arithmetic<br>Mode (AM)      | 50-51 | IRM: Rounding modes<br>"00": Round toward Zero (RZ)<br>"01": Round toward Plus infinity (RP)<br>"10": Round toward Minus infinity (RM)<br>"11": Round to Nearest even (RN)                                                                            |

|                              | 52    | DIV: Divide exception mask                                                                                                                                                                                                                            |

|                              |       | "0": When a divide exception is detected, no interrupt occurs.<br>"1": When a divide exception is detected, a divide exception<br>interrupt is generated.                                                                                             |

|                              | 53    | FOF: Floating-point overflow mask<br>"0": When a floating-point overflow is detected, no interrupt<br>occurs.<br>"1": When a floating-point overflow is detected, a floating-point                                                                    |

| PEM)                         | 54    | overflow interrupt is generated.<br>FUF: Floating-point underflow mask                                                                                                                                                                                |

| tion mask (J                 |       | "0": When a floating-point underflow is detected, no interrupt<br>occurs.<br>"1": When a floating-point underflow is detected, a floating-point<br>underflow interrupt is generated.                                                                  |

| Program exception mask (PEM) | 55    | XOF: Fixed-point overflow mask<br>"0": When a Fixed-point overflow is detected, no interrupt occurs.<br>"1": When a Fixed-point overflow is detected, a fixed-point<br>overflow interrupt is generated.                                               |

|                              | 56    | <ul><li>INV: Invalid operation exception mask</li><li>"0": When an invalid operation exception is detected, no interrupt occurs.</li><li>"1": When an invalid operation exception is detected, an invalid operation interrupt is generated.</li></ul> |

|                              | 57    | INE: Inexact exception mask<br>"0": When an inexact exception is detected, no interrupt occurs.<br>"1": When an inexact exception is detected, an inexact interrupt is<br>generated.                                                                  |

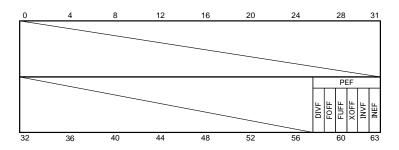

### Table 3-3 Process Status Word (3/3)

| Class              | PSW | Meaning                                                                                                                                                                                                                                                                |

|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | bit |                                                                                                                                                                                                                                                                        |

|                    | 58  | <ul> <li>DIV: Divide exception flag</li> <li>"0": No divide exception has occurred since the last time this flag was reset.</li> <li>"1": A divide exception has occurred since the last time this flag was reset.</li> </ul>                                          |

|                    | 59  | FOFF: Floating-point overflow flag<br>"0": No floating-point overflow exception has occurred since the<br>last time this flag was reset.<br>"1": A floating-point overflow exception has occurred since the last<br>time this flag was reset.                          |

| lag (PEF)          | 60  | <ul><li>FUFF: Floating-point underflow flag</li><li>"0": No floating-point underflow exception has occurred since the last time this flag was reset.</li><li>"1": A floating-point underflow exception has occurred since the last time this flag was reset.</li></ul> |

| Program flag (PEF) | 61  | XOFF: Fixed-point overflow flag<br>"0": No fixed-point overflow exception has occurred since the last<br>time this flag was reset.<br>"1": A fixed-point overflow exception has occurred since the last<br>time this flag was reset.                                   |

|                    | 62  | <ul><li>INVF: Invalid operation exception flag</li><li>"0": No invalid operation exception has occurred since the last time this flag was reset.</li><li>"1": An invalid operation exception has occurred since the last time this flag was reset.</li></ul>           |

| Note:              | 63  | <ul><li>INEF: Inexact exception flag</li><li>"0": No inexact exception has occurred since the last time this flag was reset.</li><li>"1": An inexact exception has occurred since the last time this flag was reset.</li></ul>                                         |

#### Note:

•Branch trap interrupt is triggered by the branch instruction (BC/BCS/BCF/BSIC/BCR) that is firstly encountered.

• In the branch trap mode, it's guaranteed that the interrupt happens after completing the preceding instructions and the trigger branch instruction itself.

•VW flags may be overly set even when the corresponding vector register(s) is not actually modified. Writing data to vector registers by other than execution of vector instructions is not taken account about these flags (e.g. access from the host).

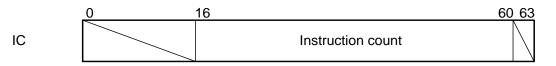

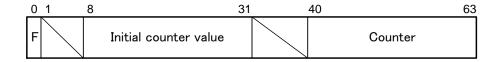

## 3.2.2. Instruction Counter (IC)

The instruction counter(IC) indicates the address of the instruction currently being executed on the VE core. Upper 16 bits and lower 3 bits of this register are always 0. Each core has one IC.

Figure 3-2 Instruction counter

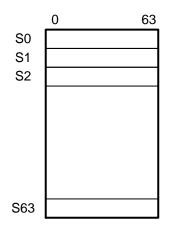

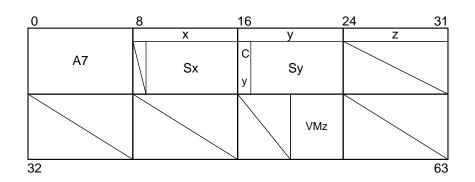

#### 3.2.3. Scalar Register (S)

Each core has 64 scalar registers (S) of 64 bits, denoted by S0, S1 ... S63

The scalar registers are used as base or index registers for address calculations, and also as operands of many instructions.

Figure 3-3 Scalar register

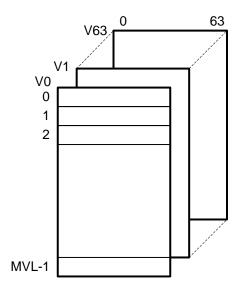

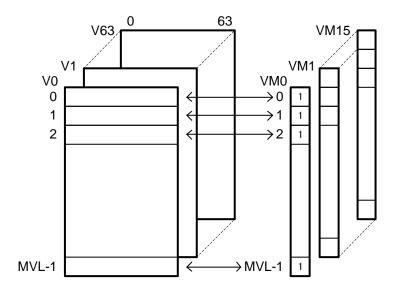

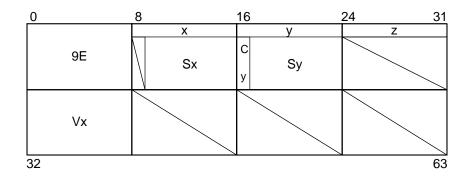

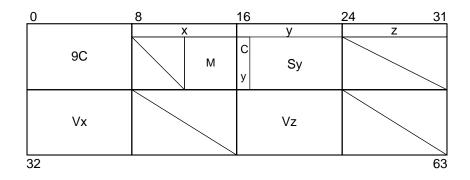

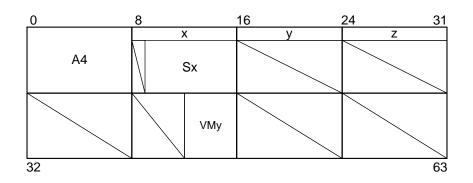

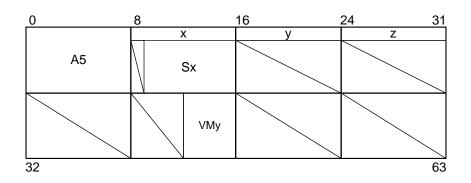

#### 3.2.4. Vector Register (V)

V(Vector Register) is a vector of 64bit registers of the length of MVL. Each core has 64 vector registers denoted by V0, V1 ... V63.

Each 64 bit register in a vector register is called a vector element, or simply an element. Elements are numbered 0, 1 ... MVL-1 sequentially.

Aurora has various vector instructions such as arithmetic operations between/amongst vector registers, data transfer operations between vector registers and the main memory. The number of elements handled by a vector instruction is specified by the VL (Vector Length) register.

Figure 3-4 Vector register (V)

Note:

•MVL in the SX-Aurora TSUBASA generation 1 is 256.

•In some SX-Aurora documents V0,V1,V2... may be denoted as VR0,VR1,VR2...

·Vector instructions are listed below.

- Vector load/store and move Instructions

- Vector fixed-point arithmetic instructions

- Vector logical operation instructions

- Vector shift operation instructions

- Vector floating-point arithmetic instructions

- Vector reduction instructions

- Vector iterative operation instructions

- Vector merger operation instructions

- Vector mask operation instructions

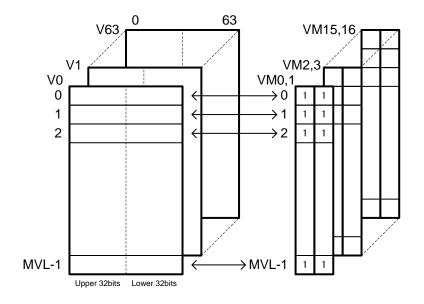

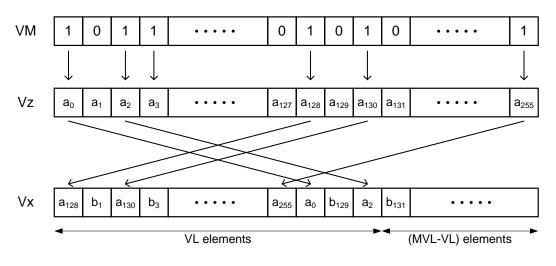

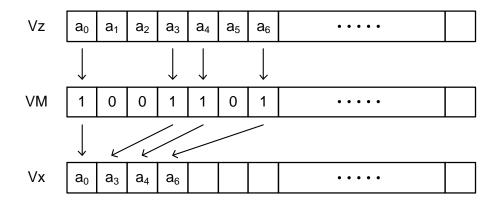

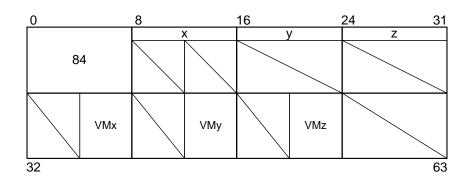

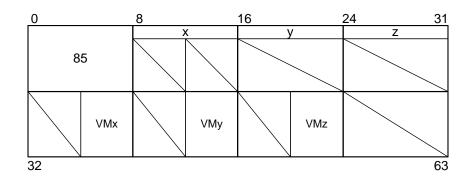

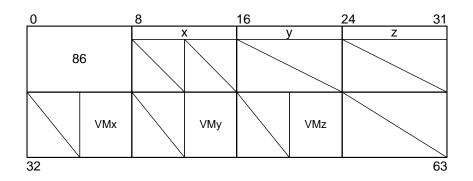

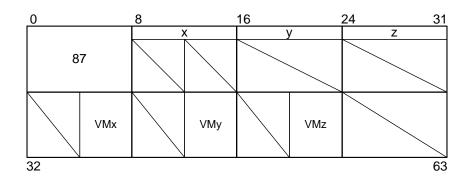

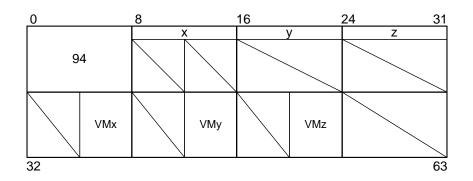

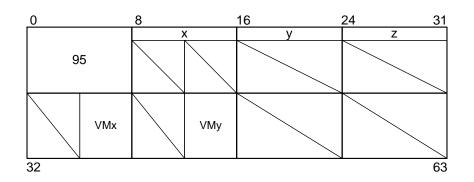

#### 3.2.5. Vector Mask Register (VM)

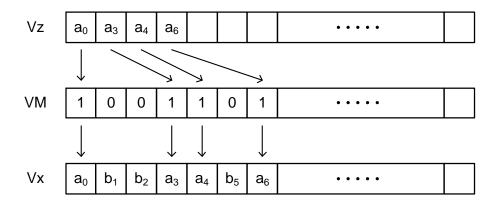

A VM is a register of the length of MVL to store vector mask data. Each core has 16 VMs denoted as VM0, VM1... VM15. The VM0 is regarded as a special one in that all bits are hardwired to 1 and cannot be modified (hardware ignores writes to the VM0).

A vector instruction with a mask field is element-maskable. Usually only one VM is specified by the mask field in the instruction. Each bit of a VM sequentially corresponds to a vector element, that is, only the vector elements enabled by corresponding VM bits (=1) will be referred to and/or modified, while the other elements will stay untouched. No exceptions will be detected for the elements that are not enabled by the corresponding VM bits.

Vector instruction with the 'packed data' format may employ two consecutive VMs starting from an even-numbered one. With packed data operations, the first and second VMs are for the upper and lower 32-bits of a vector element respectively, that is, a packed instruction can have different masks for its 32bit halves independently. Note that when VM0 is specified as the first one, the second VM is then exceptionally treated as VM0, whose all bits are always one.

VM registers can be the result operand of vector mask logical instructions or vector mask forming instructions. VM's value can be transferred to S registers and vice versa.

Figure 3-5 Correspondence of V and VM (non-packed data)

Figure 3-6 Correspondence of V and VM (packed data)

Note:

$\cdot$  MVL for the Aurora generation 1 is 256.

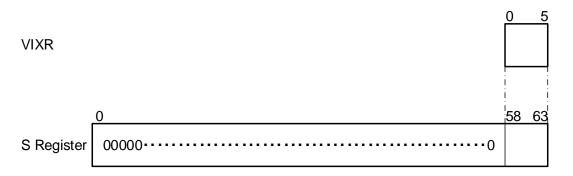

### 3.2.6. Vector Index Register (VIXR)

VIXR is a 6-bit register used as an index for indirect vector register access. Each core has one VIXR.

An instruction to transfer data between the VIXR and an S register (LVIX) is provided.

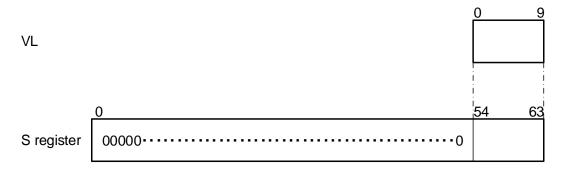

## 3.2.7. Vector Length Register (VL)

VL holds the vector element count (vector length) of vector operations to be executed. A VL is provided in each core.

The maximum vector length (MVL) is the maximum value to be set to the VL. When a larger value than MVL is given to the VL, an exception is raised and the result of the operation is undefined.

When VL=0, vector instructions are treated as NOP.

There are instructions to transfer data between VL and S registers (LVL and SVL).

### Figure 3-8 Vector length register

Note:

•MVL in the Aurora generation 1 is 256. A 10bit register is equipped for the VL.

•When a VL value more than MVL is given by an LVL instruction, an illegal data format exception will be generated, while there are some exceptional cases on the MVL operation. See also Chapter 6 for the details.

#### 3.3. System Registers

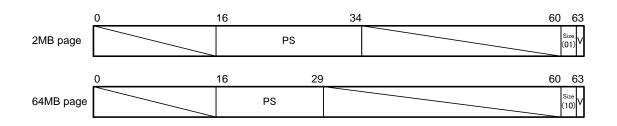

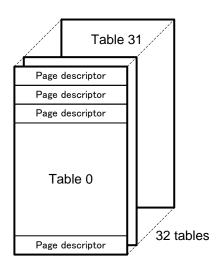

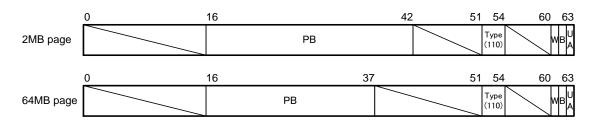

#### 3.3.1. Address Translation Buffer (ATB)

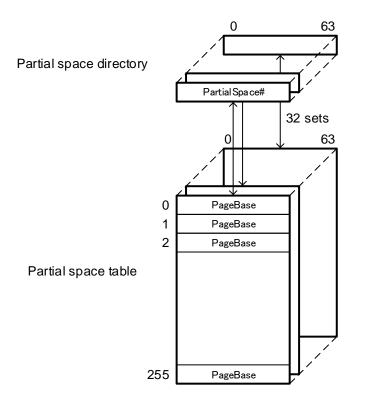

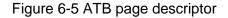

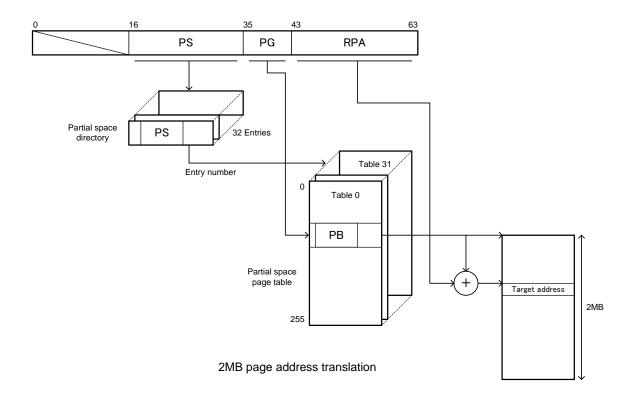

ATB is used for address translation from a VE memory virtual address to a VE memory absolute address. The ATB is composed of 32 entries of partial space directory and 32 partial space page tables. The partial space directories hold base VE memory virtual addresses and attribute information for the partial space. The partial space page tables hold base VE memory absolute addresses and attribute information for the partial space of 256 pages composing a partial space.

Details of ATB and its operation are described in Chapter 5.

Figure 3-9 Address translation buffer

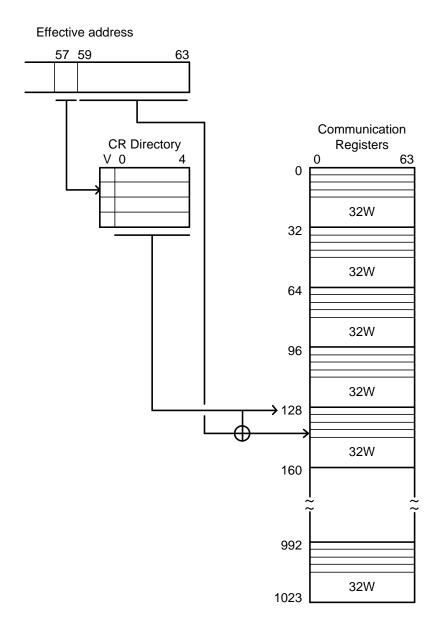

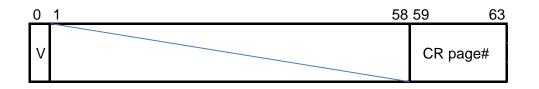

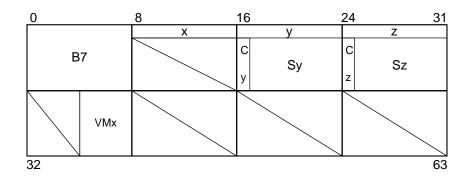

### 3.3.2. Communication Register Directory (CRD)

The CRD is used to translate an effective CR address to physical CR address on a CR access from VE cores. The CRD is composed of 4 entries, and each core has one CRD.

The details of CRD and its operation are described in Chapter 3.3.3 Communication register.

| V | 0        | 4 |

|---|----------|---|

|   | CR index | { |

|   | CR index | 7 |

|   | CR index | 2 |

|   | CR index | ( |

Figure 3-10 Communication register directory

#### 3.3.3. Communication Register (CR)

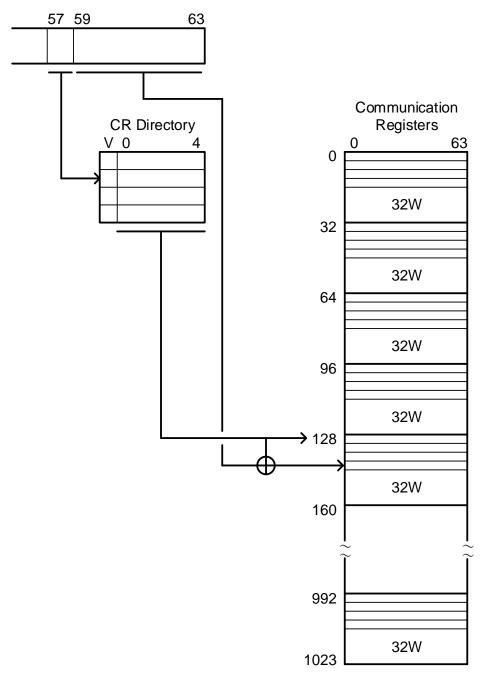

CRs are 64-bit registers used for control of exclusive execution or synchronous operation among VE cores. There are 1024 CRs in each VE node. CRs are addressed by sequential number 0 to 1023, forming 32 CR pages, 32 CRs for each page.

The communication register directory (CRD) is for address translation from an effective address to CR address on accessing CR from VE core. Each core has one CRD. A CRD has 4 entries, and each entry has a valid bit and the index to its target CR page.

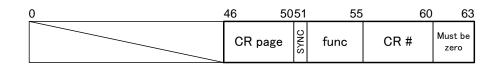

There are instructions to access CR from a VE core (LCR, SCR, TSCR and FIDCR).

At a CR access, firstly CRD is referred to with the effective address's bit 57-58 as the index and its valid bit is checked. Then if it hits on the CRD, a physical CR address is generated with the effective address bit 59-63 and its base address is obtained from the entry. When the valid bit is '0', a memory access exception will occur at an access to the CR page.

Effective address

Figure 3-11 Communication register and communication register directory

Note:

•The base address (index) of a CR page is equivalent to the upper 5-bits of 10-bit CR address.

•The CRD has four entries to CR pages. A VE core can access maximum 128 CRs without updating the CRD.

·Bit 0-56 of an effective address is ignored at CR accesses (should be zero.)

## **3.4. Performance Counters**

SX-Aurora TSUBASA provides performance monitor counters (PMCs) shown below, for each core. These are default performance indicators and may change due to other settings

| PMC    | Target event                                    |

|--------|-------------------------------------------------|

| 51/000 |                                                 |

| PMC00  | Execution count (EX)                            |

| PMC01  | Vector execution count (VX)                     |

| PMC02  | Floating point data element count (FPEC)        |

| PMC03  | Vector elements count (VE)                      |

| PMC04  | Vector execution clock count (VECC)             |

| PMC05  | L1 cache miss clock count (L1MCC)               |

| PMC06  | Vector elements count 2(VE2)                    |

| PMC07  | Vector arithmetic execution clock count (VAREC) |

| PMC08  | Vector load execution clock count (VLDEC)       |

| PMC09  | Port conflict clock count (PCCC)                |

| PMC10  | Vector Load Packet Count (VLPC)                 |

| PMC11  | Vector load element count (VLEC)                |

| PMC12  | Vector load cache miss element count (VLCME)    |

| PMC13  | Fused multiply add element count (FMAEC)        |

| PMC14  | Power throttling clock count (PTCC)             |

| PMC15  | Thermal throttling clock count (TTCC)           |

## 4. Data Format

This chapter describes the data formats and how the operations are performed on data. The source operand is the input data source of an instruction which may be a scalar register, immediate value, or vector register. The destination register may be a scalar register or vector register.

## 4.1 Data format

## 4.1.1 Fixed-point data

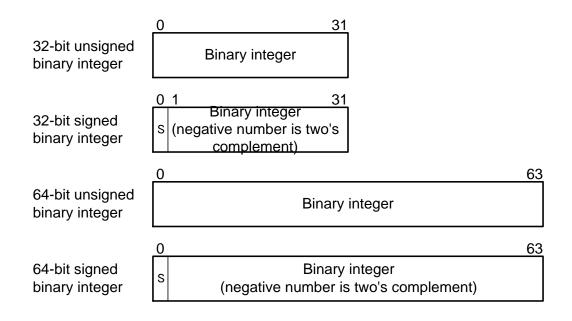

These four types of fixed point integer are supported.

In a signed binary integer, the leftmost bit represents the sign; 0 means positive and 1 is negative. A negative integer is represented in the form of the complement of two.

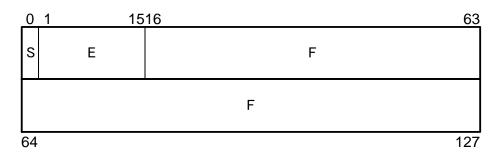

#### 4.1.2 Floating-Point Data

Single-precision data format (32bit), double-precision data format (64bit) and quadruple-precision floating-point data format (128bit) complying with the IEEE754 standards are supported.

(a) Single precision floating-point data

| 0 | 1 | 89 |   | 31 |

|---|---|----|---|----|

| s | E |    | F |    |

The single-precision data format is composed of a 1bit sign (S), 8bit exponent (E) and a 23bit fraction part (F).

•The exponent part (E) of single-precision data format is an 8bit unsigned binary number and the representation of bias value = 127 to correspond to -127 to 128. Accordingly, although exponent range is from 0 to 255, the exponent range excluding the bias is from -126 (Emin) to +127 (Emax). The exponent part is used to represent the special values shown below when its value is 0 or 255.

•The fraction (F) part contains one hidden bit.

- ① NaN if E=255 and F $\neq$ 0

- ②  $(-1)^{s} \cdot \infty$  if E=255 and F=0

- (3)  $(-1)^{s} \cdot 2^{E \cdot 127} \cdot (1.F)$  if 0 < E < 255

- ④  $(-1)^{s} \cdot 0$  if E = 0 ..... Signed zero

(b) Double precision floating-point data

The double-precision data format is composed of a 1bit sign part (S), an 11bit exponent part (E) and a 52bit fraction part (F).

•The exponent part (E) is an 11bit unsigned binary and the representation of bias value = 1023 to correspond to -1023 to 1024. Accordingly, although exponent range is from 0 to 2047, the exponent range excluding the bias is from -1022 (Emin) to +1023 (Emax), because the exponent part is used to represent the special values shown followings when the part value is 0 or 2047.

$\cdot$  The fraction (F) part contains one hidden bit. Therefore, values represented in 64bit double precision format are as shown.

①NaN if E = 2047 and F≠0 ②(-1)<sup>s</sup>·∞ if E = 2047 and F=0 ③(-1)<sup>s</sup>·2<sup>E-1023</sup>·(1.F) if 0 < E < 2047 ④(-1)<sup>s</sup>·0 if E = 0 ...... Signed Zero (c) Quadruple precision floating-point data

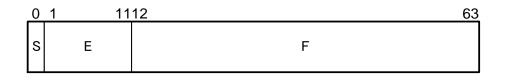

The quadruple-precision data format is composed of a 1bit sign part (S), a 15bit exponent part (E) and a 112bit fraction part (F).

•The exponent part (E) is a 15bit unsigned binary and the representation of bias value = 16383 to correspond to -16383 to 16384. Accordingly, although exponent range is from 0 to 16383, the exponent range excluding the bias is from -16382 (Emin) to +16383 (Emax), The exponent part is used to represent the special values when the part value is 0 or 32767. The cardinal number of exponent part is 2.

•The fraction (F) part contains one hidden bit. Therefore, values represented in 128bit double precision format are as shown.

①NaN if E = 32767 and F≠0 ②(-1)<sup>s</sup>·∞ if E = 32767 and F=0 ③(-1)<sup>s</sup>·2<sup>E-16383</sup>·(1.F) if 0 < E < 32767 ④(-1)<sup>s</sup>·0 if E = 0 ..... Signed Zero

·Only scalar instructions support quadruple precision data format calculation.

#### Note:

The floating-point data format of the SX-Aurora architecture is different from the format of the IEEE754 standards in that each of the denormal numbers (E=0 and F ≠ 0) is handled as zero in the SX-Aurora architecture.

•The following two type of format are defined as the NaN:

- signaling NaN : F=0xxx...x (except F=0)

- quiet NaN : F=1xxx...x Value of xxx...x are don't care

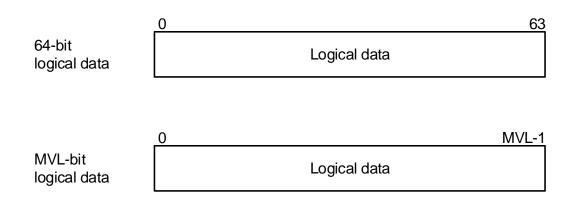

# 4.1.3 Logical Data

The following 2 type of data format are supported as logical data format.

The 64bit logical data is stored into scalar registers and vector registers. There are logical operation instructions subject to these registers.

MVL-bit vector mask is stored in a VM register. There are logical operation instructions between VM registers and vector form mask instructions to generate a MVL-bit logical data from vector register values.

# 4.2 Fixed-Point Arithmetic and Shift Operations

The following section describes major fixed-point arithmetic and shift operations. For details of instructions, refer to Chapter 7.

# 4.2.1 Addition and Subtraction

There are 6 types of addition and subtraction operations as follows.

# (a) 32bit unsigned operation

The bits 32-63 of the source operands are added or subtracted as 32bit unsigned binary integer. The bits 0-31 of the operands are ignored.

The result is stored into bits 32-63 of the destination register as a 32bit unsigned binary integer. An overflow is ignored.

The bits 0-31 of the destination register are filled with zero.

# (b) 32bit signed operation

The bits 32-63 of the source operands are added or subtracted as 32bit signed binary integer. The bits 0-31 of the operands are ignored.

The result is stored into bits 32-63 of the destination register as a 32bit signed binary integer. A fixed-point overflow exception will be raised when the result exceeds representable range of 32bit signed binary integer. Overflowed bit is discarded.

The bits 0-31 of the destination register are filled with extended sign of the result (bit 32) or zeros depending on the control field of the instruction.

# (c) 64bit unsigned operation

The source operands are added or subtracted as 64bit unsigned binary integer.

The result is stored into the destination register as a 64bit unsigned binary integer. An overflow is ignored.

# (d) 64bit signed operation

The source operands are added or subtracted as 64bit signed binary integer.

The result is stored into the destination register as a 64bit signed binary integer. A fixed-point overflow exception is raised when the result exceeds representable range of 64bit signed binary integer. Overflowed bit is discarded.

#### (e) Packed 32bit unsigned operation

The source operands are separated into upper 32bit and lower 32bit, and each part is added or subtracted as 32bit unsigned binary integer independently.

The results are stored into the destination register as concatenation of upper and lower 32bit unsigned binary integers. An overflow is ignored.

Either the result of the upper part or the lower part can be masked by 32bits of zero depending on the control field of instruction.

(f) Packed 32bit signed operation

The source operands are separated into upper and lower 32bits, then each part is added or subtracted as 32bit signed binary integer independently.

The results are stored into the destination register as a concatenated value of upper and lower 32bit signed binary integers. A fixed-point overflow exception is raised when any of the results exceeds representable range of 32bit signed binary integers. Overflowed bit is discarded.

Either the result of the upper part or the lower part can be masked by 32bits of zero depending on the control field of the instruction. In such a case, fixed-point overflow exception for the masked part is not detected.

#### 4.2.2 Multiplication

There are 5 types of multiplication operations as follows.

#### (a) 32bit unsigned operation

The bits 32-63 of the source operands are multiplied as 32bit unsigned binary integer. The bits 0-31 of the operands are ignored.

The result is stored into bits 32-63 of the destination register as 32bit unsigned binary integer. An overflow is ignored.

The bits 0-31 of the destination register are filled with zero.

#### (b) 32bit signed operation

The bits 32-63 of the source operands are multiplied as 32bit signed binary integer. The bits 0-31 of the operands are ignored.

The result is stored into bits 32-63 of the destination register as 32bit signed binary integer. A fixed-point overflow exception is raised when the result exceeds representable range of 32bit signed binary integer. Overflowed bits are discarded.

The bits 0-31 of the destination register are filled with extended sign of the result (bit 32) or zeros depending on the control field of the instruction.

#### (c) 32bit signed operation with bit width extension

The bits 32-63 of the source operands are extended to 64bit signed binary integer and multiplied. The bits 0-31 of the registers are ignored.

The result is stored into the destination register as 64bit signed binary integer. An overflow doesn't occur.

#### (d) 64bit unsigned operation

The source operands are multiplied as 64bit unsigned binary integer.

The result is stored into the destination register as 64bit unsigned binary integer. An overflow is ignored.

#### (e) 64bit signed operation

The source operands are multiplied as 64bit signed binary integer.

The result is stored into the destination register as 64bit signed binary integer. A fixed-point overflow exception is raised when the result exceeds representable range of 64bit signed binary integer. Overflowed bits are discarded.

# 4.2.3 Division

There are 4 types of division operations as follows.

#### (a) 32bit unsigned operation

The bits 32-63 of the source operands are divided as 32bit unsigned binary integer. The bits 0-31 of the operands are ignored.

The result is stored into bits 32-63 of the destination register as 32bit unsigned binary integer. A division exception occurs is raised when the divisor is zero, and the result of the operation is zero.

The bits 0-31 of the destination register are filled with zero.

(b) 32bit signed operation

The bits 32-63 of the source operands are divided as 32bit signed binary integer. The bits 0-31 of the operands are ignored.

The result is stored into bits 32-63 of the destination register as 32bit signed binary integer. A division exception is raised when the divisor is zero, and the result of the operation is zero. A fixed-point overflow is raised when the result exceeds representable range of 32bit signed binary integer.

The bits 0-31 of the destination register are filled with extended sign of the result (bit 32) or zeros depending on the control field of the instruction.

(c) 64bit unsigned operation

The source operands are divided as 64bit unsigned binary integer.

The result is stored into the destination register as 64bit unsigned binary integer. A division exception is raised when the divisor is zero, and the result of the operation is zero.

(d) 64bit signed operation

The source operands are divided as 64bit signed binary integer.

The result is stored into the destination register as 64bit signed binary integer. A division exception is raised when the divisor is zero, and the result of the operation is zero. A fixed-point overflow is raised when the result exceeds representable range of 32bit signed binary integer.

# 4.2.4 Comparison

There are 6 types of comparison operations as follows.

Result of comparison operation is expressed as follows. Assuming two source operands as Y and Z, the result is positive non-zero value if Y > Z. Else the result is zero if Y = Z, or negative value if Y < Z. Regardless of data format of the source operands, the result is expressed as signed integer.

#### (a) 32bit unsigned operation

The bits 32-63 of the source operands are compared as 32bit unsigned binary integer. The bits 0-31 of the operands are ignored.

The result is stored into bits 32-63 of the destination register as 32bit signed binary integer.

The bits 0-31 of the destination register are filled with zero.

#### (b) 32bit signed operation

The bits 32-63 of the source operands are compared as 32bit signed binary integer. The bits 0-31 of the operands are ignored.

The result is stored into bits 32-63 of the destination register as 32bit signed binary integer.

The bits 0-31 of the destination register are filled with extended sign of the result (bit 32) or zeros depending on the control field of the instruction.

#### (c) 64bit unsigned operation

The source operands are compared as 64bit unsigned binary integer.

The result is stored into the destination register as 64bit signed binary integer.

# (d) 64bit signed operation

The source operands are compared as 64bit signed binary integer.

The result is stored into the destination register as 64bit signed binary integer.

(e) Packed 32bit unsigned operation

The source operands are separated into upper 32bit and lower 32bit, and each part is compared as 32bit unsigned binary integer independently.

The results are stored into the destination register as the concatenation of upper and lower 32bit signed binary integers.

Either the result of the upper part or the lower part can be masked by 32bits of zero depending on the control field of instruction.

#### (f) Packed 32bit signed operation

The source operands are separated into upper 32bit and lower 32bit, then each part is compared as 32bit signed binary integer independently.

The results are stored into the destination register as the concatenation of upper and lower 32bit signed binary integers.

Either the result of the upper part or the lower part can be masked by 32bits of zero depending on the control field of instruction.

# 4.2.5 Compare and select operation

There are 4 types of compare and select operations as follows.

(a) 32bit signed operation

The bits 32-63 of the source operands are compared as 32bit signed binary integer, and selected greater value or lesser value in accordance with control field of the instruction. The bits 0-31 of the operands are ignored.

The result is stored into the bits 32-63 of the destination register as 32bit signed binary integer.

The bits 0-31 of the destination register are filled with extended sign of the result (bit 32) or zeros depending on the control field of the instruction.

#### (b) 64bit signed operation

The source operands are compared as 64bit signed binary integer, and selected greater value or lesser value in accordance with control field of the instruction.

The result is stored into the destination register as 64bit signed binary integer.

# (c) Packed 32bit unsigned operation

The source operands are separated into upper 32bit and lower 32bit, and each part is compared as 32bit unsigned binary integer, and selected greater value or lesser value in accordance with control field of the instruction independently.

The results are stored into the destination register as the concatenation of upper and lower 32bit unsigned binary integers.

Either the result of the upper part or the lower part can be masked by 32bits of zero depending on the control field of instruction.

#### (d) Packed 32bit signed operation

The source operands are separated into upper 32bit and lower 32bit, then each part is compared as 32bit signed binary integer, and selected greater value or lesser value in accordance with control field of the instruction independently.

The results are stored into the destination register as the concatenation of upper and lower 32bit signed binary integers.

Either the result of the upper part or the lower part can be masked by 32bits of zero depending on the control field of instruction.

4-14

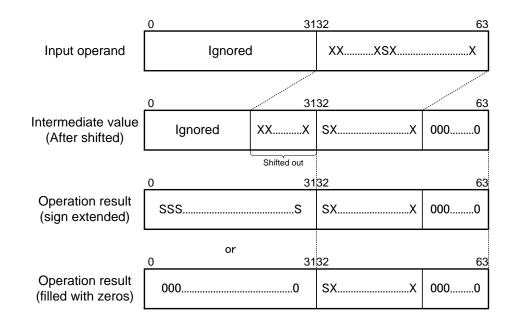

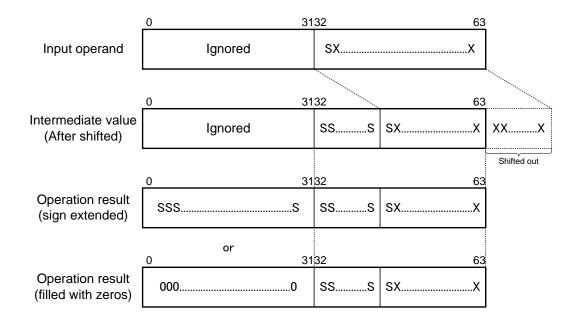

#### 4.2.6 Arithmetic Shift

There are 6 types of arithmetic shift operations as follows.

#### (a) 32bit left arithmetic shift

The shift amount and the value to be shifted are given by the bits 59-63 and the bits 32-63 of the source operands respectively. The bits 0-58 of the shift amount operand and the bits 0-31 of the value to be shifted operand are ignored.

The value is shifted left by the shift amount. The vacant bit positions are filled with zero, and the bits that would be shifted to bit 31 or upper (lower in bit position) will not be used.

The result is stored into bits 32-63 of the destination register. A fixed-point overflow exception is raised when discarded shifted out bits or the sign of the result (bit 32) includes a bit which value are not equal to the sign of the original value's bit 32.

The bits 0-31 of the destination register are filled with extended sign of the result (bit 32) or zeros depending on the control field of the instruction.

#### (b) 32bit right arithmetic shift

The shift amount and the value to be shifted are given by the bits 59-63 and the bits 32-63 of the source operands respectively. The bits 0-58 of the shift amount operand and the bits 0-31 of the value to be shifted operand are ignored.

The value is shifted right by the shift amount. The vacant bit positions are filled with the sign of the original (not-shifted) value's bit 32, and the bits that would be right-shifted out are discarded.

The result is stored into bits 32-63 of the destination register.

The bits 0-31 of the destination register are filled with extended sign of the result (bit 32) or zeros depending on the control field of the instruction.

#### (c) 64bit left arithmetic shift

The shift amount and the value to be shifted are given by the bits 58-63 and the bit 0-63 of the source operands respectively. The bits 0-57 of the shift amount operand are ignored.

The value is shifted left by the shift amount. The lower bits are filled with zero. The bits that would be left-shifted out are discarded.

The result is stored into bit 0-63 of the destination register. A fixed-point overflow exception is raised when all bits in the discarded (shifted-out) part wouldn't have been the same as the sign bit (bit 0) of the result.

# (d) 64bit right arithmetic shift

The shift amount and the value to be shifted are given by the bits 58-63 and the bit 0-63 of the source operands respectively. The bits 0-57 of the shift amount operand are ignored.

The value is shifted right by the shift amount. The vacant bit positions are filled with the sign bit of the original value (bit 0) and bits shifted out are discarded.

The result is stored into the bit 0-63 of the destination register.

(e) Packed 32bit left arithmetic shift

The source operands are separated into upper 32bits and lower 32bits, then each part may shift independently.

For the upper part, the shift amount and the value to be shifted are given by the bits 27-31 and the bits 0-31 of the source operands respectively. The bits 0-26 of the shift amount operand are ignored.

For the lower part, the shift amount and the value to be shifted are given by the bits 59-63 and the bits 32-63 of the source operands respectively. The bits 32-58 of the shift amount operand are ignored.

The results are calculated in the same fashion as (a) operation for the both part.

The results are stored into the destination register as concatenation of upper and lower 32bit signed binary integers. A fixed-point overflow exception is raised when either part of discarded shifted out bits or the sign of the result includes a bit which value are not equal to a sign bit of the initial value (bit 0 for the upper part, and bit 32 for the lower part).

Either the result of the upper part or the lower part can be masked by 32bits of zero depending on the control field of the instruction. In such a case, fixed-point overflow exception for the masked part is not detected.

(f) Packed 32bit right arithmetic shift

The source operands are separated into upper 32bits and lower 32bits, then each part may shift independently.

For the upper part, the shift amount and the value to be shifted are given by the bits 27-31 and the bits 0-31 of the source operands respectively. The bits 0-26 of the shift amount operand are ignored.

For the lower part, the shift amount and the value to be shifted are given by the bits 59-63 and the bits 32-63 of the source operands respectively. The bits 32-58 of the shift amount operand are ignored.

The results are calculated in the same fashion as (b) operation for the both part.

The results are stored into the destination register as concatenation of upper and lower 32bit signed binary integers.

Either the result of the upper part or the lower part can be masked by 32bits of zero depending on the control field of the instruction.

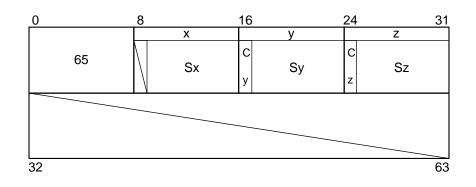

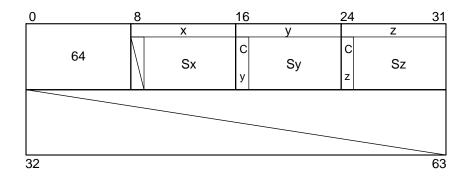

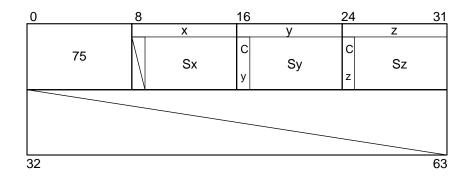

# 4.2.7 Logical Shift

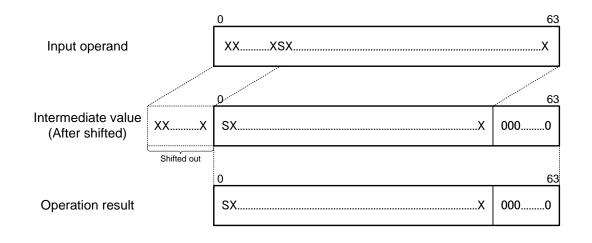

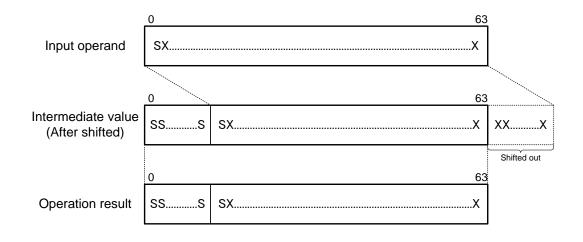

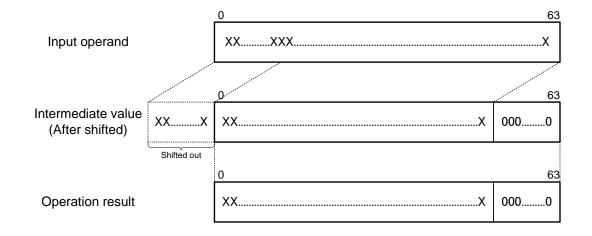

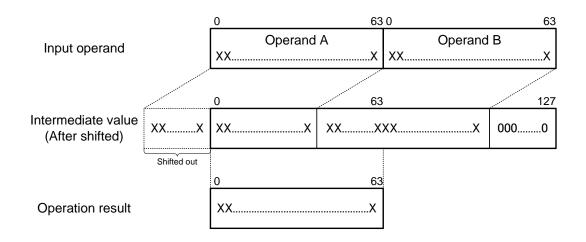

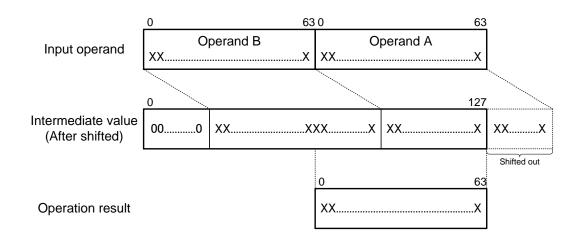

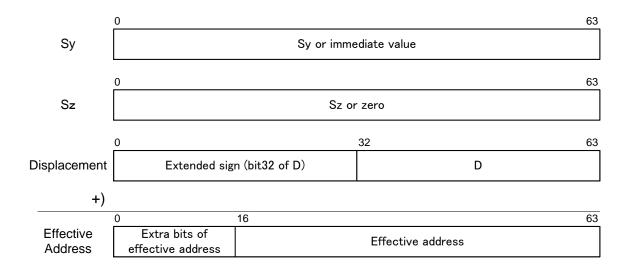

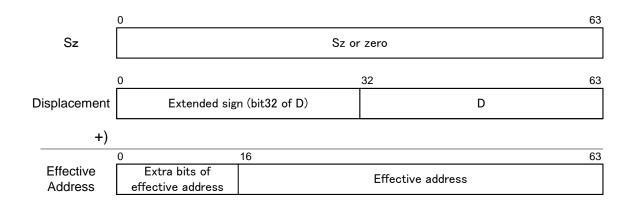

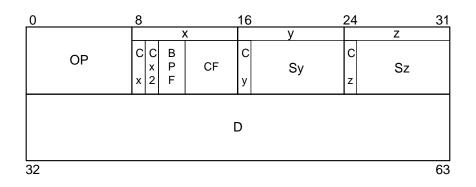

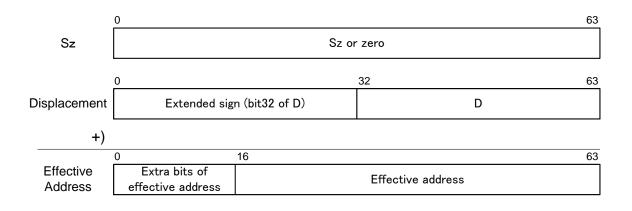

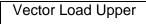

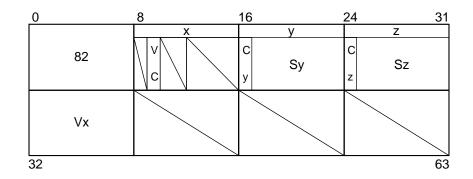

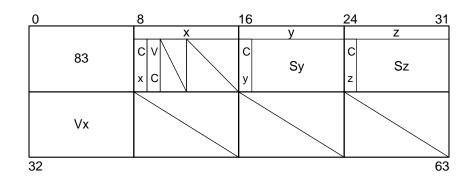

There are 6 types of logical shift operations as follows.