Sharp, G. et al. (2017) Integration Technologies for Complex Photonic Circuits. In: 8th International Conference on Metamaterials, Photonic Crystals and Plasmonics (META '17), Seoul, South Korea, 25-28 Jul 2017.

There may be differences between this version and the published version. You are advised to consult the publisher's version if you wish to cite from it.

http://eprints.gla.ac.uk/155062/

Deposited on: 5 March 2018

Enlighten – Research publications by members of the University of Glasgow\_ http://eprints.gla.ac.uk

## **Integration Technologies for Complex Photonic Circuits**

G. J. Sharp<sup>1\*</sup>, Y. Song<sup>1</sup>, N. Zhang<sup>1</sup>, C. Klitis<sup>1</sup>, V. Biryukova<sup>1</sup>, S. May<sup>1</sup>, J. McPhillimy<sup>2</sup>, M. Reza<sup>1</sup>, E. Di Gaetano<sup>1</sup>, B.M. Holmes<sup>1</sup>, M. J. Strain<sup>2</sup>, M. Sorel<sup>1</sup>

<sup>1</sup>School of Engineering, University of Glasgow, G12 8LT Glasgow, United Kingdom <sup>2</sup>Institute of Photonics, University of Strathclyde, G1 1RD Glasgow, United Kingdom <sup>\*</sup>corresponding author: graham.sharp@glasgow.ac.uk

**Abstract**-Future photonic integrated chips for quantum experiments will demand several thousand of components and a number of diverse functionalities integrated on the same chip. We will discuss some of the challenges faced by the up-scaling of photonic integrated chips with a particular emphasis on robust component trimming and heterogeneous integration of III-V devices on a silicon-on-insulator platform.

The rapid increase in the complexity of quantum experiments demands a shift from bulk optics experiments to integrated circuits that can offer larger stability, compactness and low cost. Amongst the various material platforms, silicon-on-insulator (SOI) is of particular interest thanks to its large third-order nonlinearity, technological maturity and potential for large scale manufacturing. Moreover, its large index contrast allows for the design of very small bend radii that translates into high component density, with figures already exceeding thousands of components per chip<sup>1,2</sup>.

However, component numbers and functionalities cannot indefinitely scale up if a number of issues are not effectively addressed. These include the development of algorithms, technologies and designs to mitigate the fabrication process variability, as well as manufacturing processes that allow wafer scale heterogeneous integration. The latter is of particular relevance to all those applications that require components such as optical sources, which cannot be provided by silicon. Here, we will focus on recent advances on trimming of silicon photonic components in complex circuits and on back-end integration of III-V membrane lasers by transfer printing.

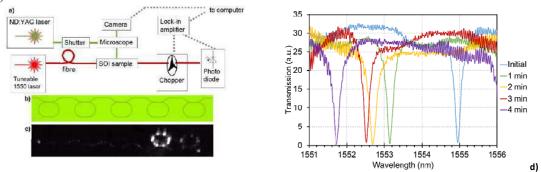

An effective way to trim optical components is to thermally cure a cladding layer on top of the silicon waveguide as a means to permanently change the effective index of the optical mode. We will discuss trimming techniques that offer long-term stability and wide tuning range through localised laser irradiation of the upper cladding (see Fig. 1).

Figures 1 a) Schematic of experimental set-up for localised trimming of SOI components using a frequency-doubled

ND:YAG laser. b) Micrograph of a racetrack resonator array and c) Racetrack array viewed in the infra-red while light is scattered from rings at resonance. d) Transmission spectra of a SOI racetrack resonator following thermal curing at 250  $^{\circ}$ C at 1 minute increments.

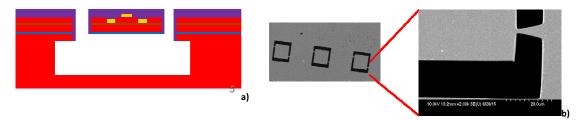

We will also present results on the transfer printing of III-V membrane devices onto silicon substrate with sub-micrometer positioning accuracy<sup>3</sup>. A notable advantage of this method, other than its scalability and precise alignment is the flexibility of the process. In fact, the bonding occurs after device fabrication, thus allowing independent fabrication processing of III-V and SOI wafers. Also, many different III-V membrane devices can be printed onto the SOI host substrate, with the potential for a wide range of heterogeneously integrated photonic devices. One such example is the integration of membrane materials with large Pockels coefficients for the development of ultra-fast electro-optic modulators.

**Figures 2** a) Schematic showing the cross-section of a membrane device. b) SEM micrographs of III-V membranes with zooming in on the mechanical support tip

The authors acknowledge support from the technical staff of the James Watt Nanofabrication Center at Glasgow University. The research is supported by the European Union *ROAM* project (grant no. 645361) and by the EPSRC *Cornerstone* project (EP/L021129/1).

## REFERENCES

- Sun J, Timurdogan E, Yaacobi A, Hosseini ES, Watts MR. Large-scale nanophotonic phased array. Nature 2013;493:195–9

- Harris NC, Steinbrecher GR, Mower J, Lahini Y, Prabhu M, Baehr-Jones T, Hochberg M, Lloyd S, Englund D. Bosonic transport simulations in a large-scale programmable nanophotonic processor. arXiv preprint 2015. arXiv:1507.03406.

- AJ Trindade, B Guilhabert, D Massoubre, D Zhu, N Laurand, E Gu, IM Watson, CJ Humphreys & MD Dawson, Nanoscale-accuracy transfer printing of ultra-thin AlInGaN light-emitting diodes onto mechanically flexible substrates Appl. Phys. Lett., vol. 103, no. 25, p. 253302, 2013